Z80P‚جک_—گفŒv

Z80P‚حZ80PLD‚ًڈب—ھ‚µ‚½‚à‚ج‚إPLD‚ةZ80‚جƒvƒچƒOƒ‰ƒ~

ƒ“ƒOƒ‚ƒfƒ‹‚ًژہ‘•‚·‚邽‚ك‚جک_—•”•i‚إ‚·پB

ƒ`ƒbƒv‚جگفŒv‚ةZ80—p‚ةٹJ”‚³‚ꂽ‘½—l‚بƒRƒ“ƒsƒ…پ[ƒ^

ƒvƒچƒOƒ‰ƒ€Œ¾Œê‚ھژg‚¦‚é‚و‚¤‚ة‚ب‚è‚ـ‚·پB

Z80‚ح8080‚ًٹg’£‚µ‚½ژd—l‚ب‚ج‚إ–½—ك‘جŒn‚à•،ژG‚إک_—

گفŒv‚ة‚¨‚¢‚ؤ‚à‘S‘ج‚جŒ©’ت‚µ‚ھˆ«‚‘ه•د‚إ‚µ‚½پB

‚µ‚©‚µ•¶ڈ‘‰»‚إ‚حک_—•ˆ‚ج‚ا‚±‚إ‰½‚ً‚µ‚ؤ‚¢‚é‚©‚ً‚·

‚®‚ة’T‚¹‚é‚و‚¤‚ة‚µ‚ـ‚µ‚½پB

PDF‚جچw“ü

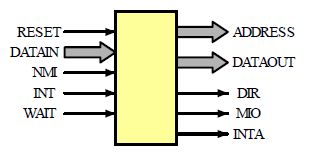

PLD ‚ج—e—ت‚ً‘ه‚«‚ژg‚¦‚éڈêچ‡‚ة‚ح”ؤ—p‚جƒvƒچƒZƒbƒT‚ً“±“ü‚µ‚ؤƒ`ƒbƒv“à‚جگ§Œن‚ًƒvƒچƒOƒ‰ƒ€‚إگفŒv‚·‚邱

‚ئ‚à‚إ‚«‚ـ‚·پBƒ`ƒbƒv‚ًŒّ—¦“I‚ةژg‚¢‚½‚¢ڈêچ‡‚âچ‚‘¬“®چى‚ً‚³‚¹‚½‚¢ڈêچ‡‚ج‘I‘ًژˆ‚ة‚ح‚ب‚è‚ـ‚¹‚ٌ‚ھƒvƒچƒOƒ‰ƒ€

‚إگفŒv‚·‚邱‚ئ‚ة‘ه‚«‚ب—e—ت‚ًژg‚ء‚ؤ‚و‚¢‚ج‚ب‚çZ80 ‚ً’m‚ç‚ب‚¢گفŒvژز‚إ‚àC Œ¾Œê‚ب‚ا‚ة‚و‚éگفŒv‚ھ‰آ”\‚ة‚ب

‚è‚ـ‚·پBZ80 ‚ج“±“ü‚ح“dژq•”•i‚جZ80 ‚ًPLD ‚إژہŒ»‚·‚邱‚ئ‚إ‚ح‚ب‚Z80 ‚جƒvƒچƒOƒ‰ƒ€‚ھ“®‚ƒvƒچƒOƒ‰ƒ~ƒ“

ƒOƒ‚ƒfƒ‹‚ًPLD “à‚ةچ\’z‚·‚邱‚ئ‚إ‚·پBZ80 ‚جƒRپ[ƒh‚ً“®‚©‚·‚½‚ك‚جک_—‚ًƒvƒچƒOƒ‰ƒ€‚ئˆêڈڈ‚ةƒ`ƒbƒv‚ة“à‘

‚·‚éک_—گفŒv‚ًچs‚¢‚ـ‚·پB

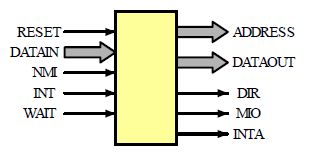

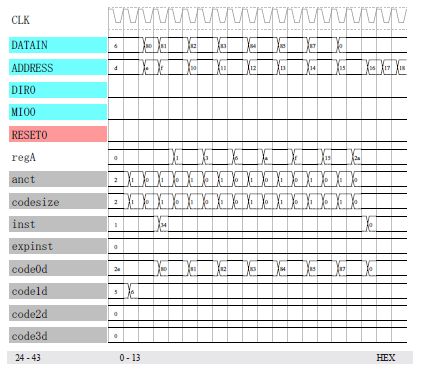

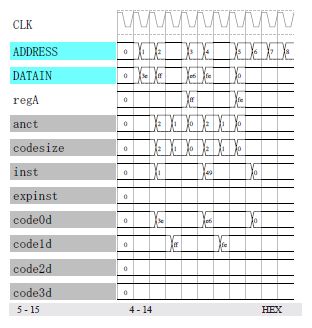

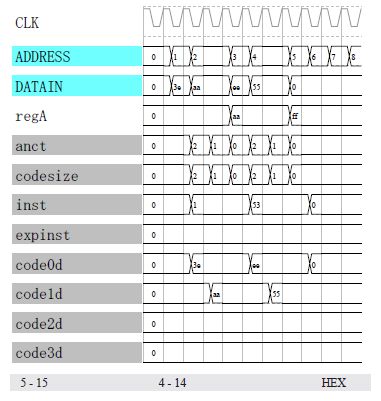

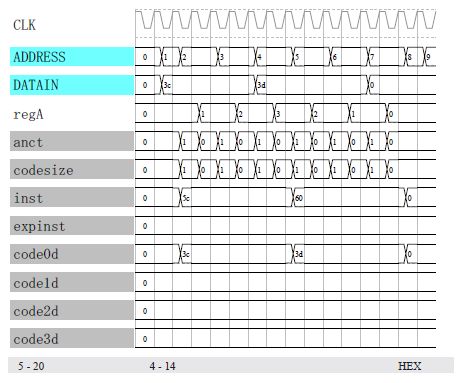

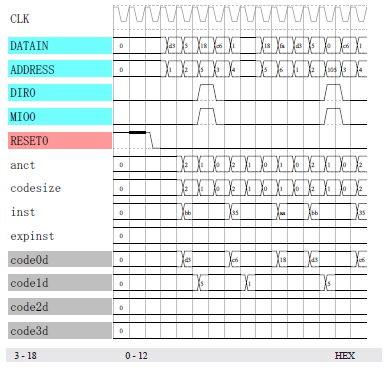

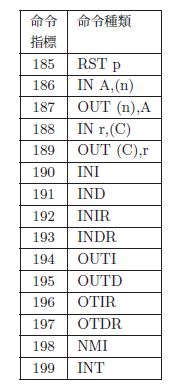

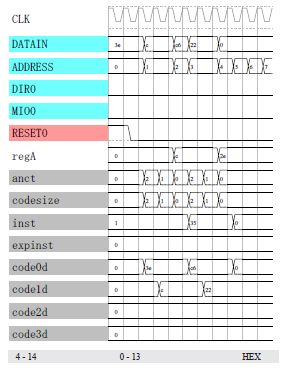

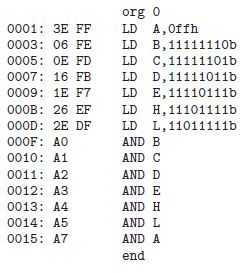

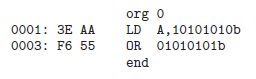

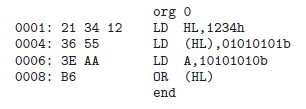

گ}1.2A

|

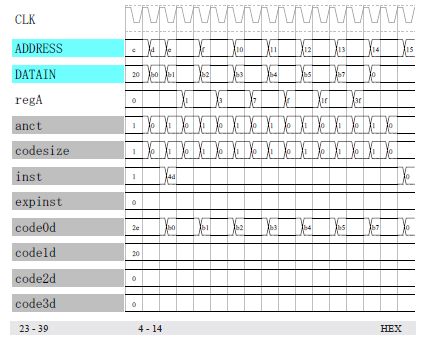

Z80 ‚ح8080 ‚ًٹg’£‚µ‚½”ؤ—p8 ƒrƒbƒgƒvƒچƒZƒbƒT‚إ‚·‚©‚çژہ—p“I‚بƒvƒچƒOƒ‰ƒ€‚ًڈ‘‚¯‚é8080 ‚ـ‚إژd—l‚ًڈ¬‚³

‚‚·‚邱‚ئ‚à‚إ‚«‚ـ‚·پBZ80 ‚جک_—گفŒv‚إ‚حژd—l‚جٹg’£‚حچs‚¢‚ـ‚¹‚ٌ‚ھ“¯‚¶ƒRپ[ƒh‚ھژہچs‚إ‚«‚邾‚¯‚جŒفٹ·‚µ‚©

چl—¶‚µ‚ـ‚¹‚ٌ“ا‚فڈ‘‚«‚ح1CLK ‚إچs‚¢‚ـ‚·‚ھWAIT ‚إگ§Œن‰آ”\‚ة‚µ‚ـ‚·پB

Z80 ‚جک_—‚حژ葱‚«‚ئ‚µ‚ؤ’ٌ‹ں‚µ‚ـ‚·‚ج‚إ•ت‚ةگفŒv‚µ‚½ک_

—‚ئ‘g‚فچ‡‚ي‚¹‚ؤژg—p‚µ‚ـ‚·‚ھژ葱‚«‚ح گ}1.2A ‚ج‚و‚¤‚ب‚à‚ج

‚إ‚·پBک_——e—ت‚حCPLD ‚ة‚ح“ü‚ç‚ب‚¢‚ھ’†ڈ¬‚جFPGA ‚ة‚ح8

ٹ„’ِ“x‚ج‹K–ح‚إ”[‚ـ‚é‚ئژv‚¢‚ـ‚·پB

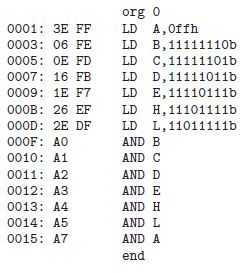

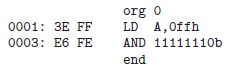

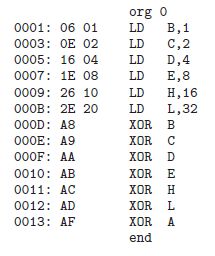

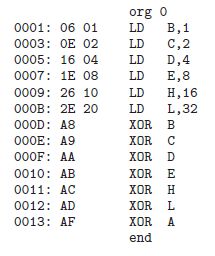

8080 ‚حA,B,C,D,E,H,L ‚ج7 Œآ‚جƒŒƒWƒXƒ^‚ًژ‚ء‚ؤ‚¢‚ـ‚·پB

Z80 ‚حگê—pƒŒƒWƒXƒ^Œ`ژ®‚ة‹ك‚¢ƒvƒچƒZƒbƒT‚إ‚·‚©‚牉ژZ‚حژه‚ة

A ƒŒƒWƒXƒ^‚ً‰î‚µ‚ؤچs‚¢‚ـ‚·پBA ‚ًڈœ‚ƒŒƒWƒXƒ^‚ح2 Œآ‚ًˆê‘g‚ئ‚µ‚ؤ16 ƒrƒbƒgƒŒƒWƒXƒ^‚ئ‚µ‚ؤژg‚¦‚邽‚ك16

ƒrƒbƒg‘€چى‚ھ‰آ”\‚ة‚ب‚ء‚ؤ‚¢‚ـ‚·BC,DE,HL ‚ح16 ƒrƒbƒg‚جƒپƒ‚ƒٹ”ش’n‚ًژw’è‚·‚éƒCƒ“ƒfƒbƒNƒXƒŒƒWƒXƒ^‚ة‚à

‚ب‚è‚ـ‚·پB8080 ‚ح‰آ•د–½—ك’·‚جˆê•”‚ج16 ƒrƒbƒgƒfپ[ƒ^‚à‘€چى‰آ”\‚ب8 ƒrƒbƒgƒvƒچƒZƒbƒT‚إ‚·پB8080 ‚àZ80 ‚à

ڈ‰ٹْ‚جژہ—p“I‚بƒ}ƒCƒNƒچƒvƒچƒZƒbƒT‚إ‚·“–ژ–‚حƒپƒ‚ƒٹ‚ج‘€چى‚ج‚½‚ك‚جژw’è‚ً–L•x‚ة‚·‚邱‚ئ‚â–½—ك‚جژي—ق‚ً‘‚â

‚·‚±‚ئ‚ة’چ—ح‚³‚ê‚ؤ‚¢‚ـ‚µ‚½Z80 ‚à‚»‚ج•ûŒü‚إٹg’£‚³‚ê‚ؤ‚¨‚èƒCƒ“ƒfƒbƒNƒXƒŒƒWƒXƒ^‚جIX ‚ئIY ‚ج2 –{‚ئ–L•x

‚ب–½—ك‚ھ’ا‰ء‚³‚ê‚ـ‚µ‚½پB‚ـ‚½ڈ]—ˆ‚ج8080 ‚جƒŒƒWƒXƒ^‚ً•\‚ئ— ‚جگط‚è‘ض‚¦ژ®‚إژg‚¦‚é‚و‚¤‚ة‚µ‚ؤƒŒƒWƒXƒ^گ”‚ً

‘‚₵‚ؤ‚¢‚ـ‚·پBŒ»چف‚جƒvƒچƒZƒbƒT‚حC Œ¾Œê‚ب‚ا‚إڈ‘‚©‚ꂽƒvƒچƒOƒ‰ƒ€‚ھچ‚‘¬‚ة’لڈء”ï“d—ح‚إژہچs‚·‚邱‚ئ‚ً

‹پ‚ك‚ç‚ê‚ؤ‚¢‚ـ‚·‚ج‚إگV‹K‚ةگفŒv‚·‚éڈêچ‡‚حƒŒƒWƒXƒ^گ”‚ً‘‚₵‚ؤƒپƒ‚ƒٹ‘€چى‚ًŒ¸‚炵چإڈ¬Œہ“x‚ج–½—ك‚ًژہ‘•‚µ

‚ؤƒvƒچƒZƒbƒT‚ً’Pڈƒ‚ة‚µ‚ـ‚·پBZ80 ‚جڈêچ‡‚ح8080 ‚ًٹg’£‚µ‚½ژ–ڈî‚ب‚ا‚à‚ ‚背ƒWƒXƒ^گ”‚حڈ‚ب‚¢‚ھ–½—ك‚جژي—ق

‚ھ‘½‚¢•،ژG‚بƒvƒچƒZƒbƒT‚ئŒ¾‚¦‚ـ‚·پB

PLD ‚ج’†‚إƒvƒچƒOƒ‰ƒ€‚ً“®‚©‚·‚½‚ك‚جک_—گفŒv‚ًچs‚¢‚ـ‚·‚ھˆê”ت“I‚بƒRƒ“ƒsƒ…پ[ƒ^‚جگفŒv‚ئ‚حٹضŒW‚ ‚è‚ـ‚¹

‚ٌ’تڈي‚جک_—گفŒv‚ج’†‚ةƒvƒچƒOƒ‰ƒ€‚ھژہچs‚إ‚«‚éٹآ‹«‚ئ‚µ‚ؤ‚جƒvƒچƒZƒbƒT‚ً“±“ü‚·‚邱‚ئ‚إƒvƒچƒOƒ‰ƒ€‚جگفŒvٹآ

‹«‚à‘ه‚«‚بˆس–،‚إک_—گفŒv‚ةٹـ‚ـ‚ê‚é‚ئچl‚¦‚ؤ‚¢‚ـ‚·‚ج‚إک_—گفŒv‚ج‚ذ‚ئ‚آ‚ج•û–@‚ئ‚µ‚ؤ‚جƒvƒچƒOƒ‰ƒ€گفŒv‚إ‚

‚èƒvƒچƒOƒ‰ƒ€‚ً“®‚©‚·‚½‚ك‚جƒvƒچƒZƒbƒT‚ج“±“ü‚ئچl‚¦‚ؤ‚¢‚ـ‚·پB

ƒvƒچƒOƒ‰ƒ€‚ً“®‚©‚·‚ئ‚حƒvƒچƒOƒ‰ƒ€ƒJƒEƒ“ƒ^‚ھ“®‚¢‚ؤ‚¢‚é‚ئŒ¾‚¤‚±‚ئ‚إƒvƒچƒZƒbƒT‚ج•s‰آŒ‡‚ج—v‘f‚حƒvƒچƒOƒ‰

ƒ€ƒJƒEƒ“ƒ^‚ة‚ب‚è‚ـ‚·پBƒvƒچƒOƒ‰ƒ€‚إ“®‚‘•’u‚ً—v–ٌ‚·‚é‚ئƒvƒچƒOƒ‰ƒ€‚ة‚و‚ء‚ؤƒvƒچƒOƒ‰ƒ€ƒJƒEƒ“ƒ^‚ج’l‚ً•د‚¦

‚ب‚ھ‚ç–³Œہ‚ة“®‚¢‚ؤ‚¢‚é‚à‚ج‚ئŒ¾‚¦‚ـ‚·پB‚و‚ء‚ؤƒvƒچƒOƒ‰ƒ€ƒJƒEƒ“ƒ^‚جگi‚ق‘¬“x‚ھƒvƒچƒZƒbƒT‘S‘ج‚جگ«”\‚ًچ¶‰E

‚·‚邱‚ئ‚ة‚ب‚è‚ـ‚·پBƒvƒچƒZƒbƒT‚جژہچs’iٹK‚إ‚حƒvƒچƒOƒ‰ƒ€‚ئ‚حƒvƒچƒZƒbƒT‚جŒإ—L‚ج–½—ك‚جکA‚ب‚è‚إ‚·پBƒvƒچƒO

ƒ‰ƒ€ƒJƒEƒ“ƒ^‚حƒvƒچƒZƒbƒT‚ھ–½—ك‚ًڈ‡”ش‚ة“ا‚فڈo‚·‚½‚ك‚ة“®‚¢‚ؤ‚¢‚ـ‚·پBƒvƒچƒZƒbƒT‚جژ‚آٹî–{“I‚ب–½—ك‚ح‰‰

ژZپAƒfپ[ƒ^ˆع“®پA•ھٹٍ‚إ‚ ‚é‚ئژv‚¢‚ـ‚·“ء‚ة•ھٹٍ‚حƒvƒچƒOƒ‰ƒ€‚ھک_—“I‚ة“®‚‚½‚ك‚ة•K—v‚إ‚·–½—ك‚ج‘½‚‚ح‰‰ژZ

‚âƒfپ[ƒ^ˆع“®‚إ‚·ƒvƒچƒOƒ‰ƒ€‚ح‚±‚ê‚ç‚ج–½—ك‚ًکA‚ث‚ؤ‹پ‚ك‚ç‚ꂽ‹@”\‚ً‰ت‚½‚µ‚ـ‚·پB

ƒvƒچƒZƒbƒT‚حƒvƒچƒOƒ‰ƒ€‚جٹˆ–ô‚ج•‘‘ن‚ة‚ب‚é‚ي‚¯‚إ‚·‚ھ‚ا‚؟‚ç‚©‚ئŒ¾‚¤‚ئ— •û‚إ‚·C Œ¾Œê‚ب‚ا‚إƒvƒچƒOƒ‰ƒ€

‚ً‘g‚قڈêچ‡‚ة‚حƒvƒچƒZƒbƒT‚جژ‚آƒŒƒWƒXƒ^‚â–½—ك‚جژي—ق‚ب‚ا‚ح’m‚ç‚ب‚‚ؤ‚à‚و‚¢‚©‚ç‚إ‚·پBڈ‰ٹْ‚جƒvƒچƒZƒbƒT‚ح

–½—ك‚جژي—ق‚ً‘‚₵‚ؤƒAƒZƒ“ƒuƒٹŒ¾Œê‚إ‚جƒvƒچƒOƒ‰ƒ€‚ًڈ¬‚³‚چى‚è‚â‚·‚‚µ‚و‚¤‚ئ‚µ‚ؤ‚¢‚ـ‚µ‚½‚ھƒ†پ[ƒU‚حC

Œ¾Œê‚ب‚ا‚جƒvƒچƒOƒ‰ƒ€‚ةˆعچs‚µ‚ؤ‚¨‚èƒRƒ“ƒpƒCƒ‰‚ح‚ا‚جƒvƒچƒZƒbƒT‚ة‚à‚ ‚é‚و‚¤‚ب–½—ك‚ًڈ‚ب‚ژg‚ء‚ؤچ\گ¬‚µ‚ؤ

‚¢‚½‚ج‚إ‰ك“nٹْ‚جƒvƒچƒZƒbƒT‚ح–³—p‚ة‘ه‚«‚‚ب‚ء‚ؤ‚µ‚ـ‚¢•ûŒü‚ھ“]ٹ·‚³‚ê‚ـ‚µ‚½پBƒ}ƒCƒNƒچƒvƒچƒZƒbƒT‚ج’aگ¶‚ج

‚«‚ء‚©‚¯‚ح“d‘ى—p‚جƒvƒچƒZƒbƒT‚ج–½—ك‚ج“®چى‚ھ•،ژG‚ب‚½‚ك‚ةƒvƒچƒZƒbƒT‚جگفŒv‚ةژٹش‚ھ‚©‚©‚é‚ج‚إ–½—ك‚ج“®چى‚ً

’Pڈƒ‚ة‚µ‚ؤƒvƒچƒZƒbƒT‚جگفŒv‚ً‘پٹْ‚ةڈI‚ي‚点‚ؤ‚»‚ج•د‚ي‚è‚ة•،ژG‚ب“d‘ى‚ج“®چى‚ج•û‚ح–½—ك‚ًکA‚ث‚½ƒvƒچƒOƒ‰ƒ€

‚ةڈ‘‚¯‚خ‚و‚¢‚ئŒ¾‚¤”‘z‚¾‚ء‚½‚炵‚¢‚إ‚·پBٹْ‘ز‚³‚ê‚éژdژ–‚ة‘خ‚µ‚ؤ‘¬“x‚ھڈ\•ھ‚ب‚ئ‚«‚حƒvƒچƒZƒbƒT‚جچ\‘¢‚ح’P

ڈƒ‚ة‚µ‚ؤƒvƒچƒOƒ‰ƒ€‚ج•‰’S‚ھ‘ه‚ة‚ب‚葬“x‚ھ•sڈ\•ھ‚ج‚ئ‚«‚حƒvƒچƒZƒbƒT‚جچ\‘¢‚ً•،ژG‚ة‚µ‚ؤ‘خ‰‚·‚é‚ئŒ¾‚¤ŒJ‚è

•ش‚µ‚ة‚ب‚é‚و‚¤‚إ‚·پBƒvƒچƒZƒbƒT‚ھچHڈê‚إگ¶ژY‚³‚ê‚ؤ‚¢‚½‚ئ‚«‚ح‚±‚ج‚و‚¤‚ب‚±‚ئ‚إ‚ ‚ء‚½‚ئژv‚¢‚ـ‚·‚ھ‘ه—تگ¶ژY

•i‚إ‚ب‚‚ب‚ء‚½ڈêچ‡‚ة‚ح‚ا‚ج‚و‚¤‚ب‚±‚ئ‚ھŒ¾‚¦‚é‚©‚ح‚ي‚©‚è‚ـ‚¹‚ٌپB

ƒfپ[ƒ^‚ج’u‚«ڈêڈٹ‚إ‚ ‚郌ƒWƒXƒ^‚âƒپƒ‚ƒٹ‹َٹش‚ئƒfپ[ƒ^‘€چى‚ج‚½‚ك‚ةƒvƒچƒZƒbƒT‚جژ‚ء‚ؤ‚¢‚é–½—ك‚ھ‚ ‚è‚ـ‚·

‘¼‚ة–½—ك‚جŒ‹‰ت‚ً‹L‰¯‚·‚éƒtƒ‰ƒO‚ب‚ا‚إ‚·پBZ80 ‚ب‚ا‚جڈ‰ٹْ‚جƒvƒچƒZƒbƒT‚ة‚ح‚ ‚è‚ـ‚¹‚ٌ‚ھƒپƒ‚ƒٹ‹َٹش‚ھ‘ه‚«‚

‚ب‚é‚ئƒپƒ‚ƒٹٹا—‚ج‹@چ\‚ًژ‚آ‚à‚ج‚à‚ ‚è‚ـ‚·پB‚ـ‚½ƒvƒچƒOƒ‰ƒ€‚ًژ•ھٹ„‚إژہچs‚·‚é‹@چ\‚ًژ‚آƒvƒچƒZƒbƒT‚à‚

‚è‚ـ‚·پB‚±‚ê‚ç‚ح‚ذ‚ئ‚آ‚جƒvƒچƒZƒbƒT‚ة•،گ”‚جƒvƒچƒOƒ‰ƒ€‚ًˆہ‘S‚ةژہچs‚·‚邽‚ك‚ةگف‚¯‚ç‚ꂽ‹@چ\‚ب‚ج‚إ‚·‚ھ

PLD ‚ةژہ‘•‚·‚éƒvƒچƒZƒbƒT‚ج’P‘ج‚ة‚ح•K—v‚ج‚ب‚¢‹@”\‚¾‚ئژv‚ء‚ؤ‚¢‚ـ‚·پBPLD ‚ة‚ح—e—ت‚ج”حˆح‚ب‚ç•،گ”‚جƒvƒچ

ƒZƒbƒT‚ًژہ‘•‚إ‚«‚é‚ج‚إ’Pڈƒ‚ةŒآ•ت‚جƒvƒچƒZƒbƒT‚جŒآ•ت‚جƒپƒ‚ƒٹ‹َٹش‚ةŒآ•ت‚جƒvƒچƒOƒ‰ƒ€ژہچs‚³‚¹‚ê‚خچد‚ق‚ئژv

‚ي‚ê‚ـ‚·پB

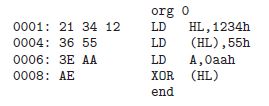

–½—ك‚ًژہچs‚·‚邽‚ك‚ة‚ح–½—ك•„‚ًŒںڈo‚µ‚ؤ–½—ك’·‚ئ–½—كژہچs‚جCLK گ”‚ً“ء’肵‚ؤ–½—ك‚جژہچsچs’ِ‚ًŒˆ’è‚·‚é

•K—v‚ھ‚ ‚è‚ـ‚·پB

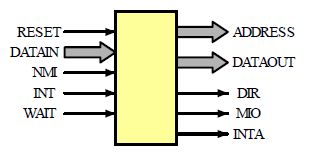

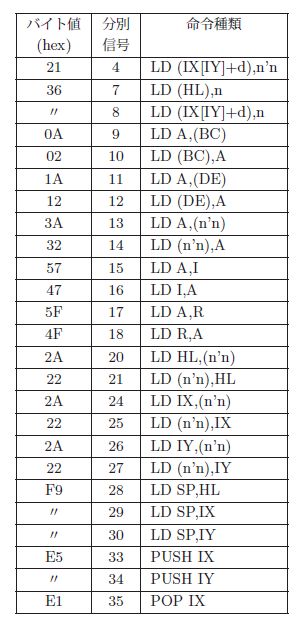

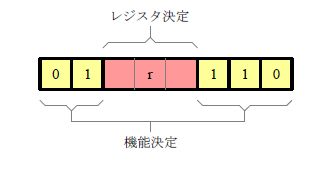

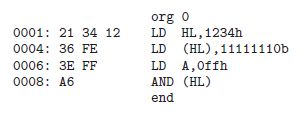

–½—ك•„‚حژہچs‚³‚ê‚é‹@”\‚ئ‚»‚ج‘خڈغ‚ئ‚ب‚郌ƒWƒXƒ^‚âƒپƒ‚ƒٹ‚ب‚ا‚ًژ¦‚µ‚ؤ‚¢‚ـ‚·—ل‚¦‚خLD r,(HL) ‚ج–½—ك•„

‚ج گ}1.5.1A ‚جڈêچ‡‚حr ‚إژ¦‚³‚ê‚é0پ`7 ‚جƒŒƒWƒXƒ^‚ج‚ا‚ê‚©‚ةHL ‚ج’l‚ً”ش’n‚ة‚µ‚½ƒپƒ‚ƒٹ‚ج“à—e‚ً“ا‚فڈo‚µ‚ؤ‹L

‰¯‚·‚é‹@”\‚ً•\‚µ‚ؤ‚¢‚ـ‚·پB

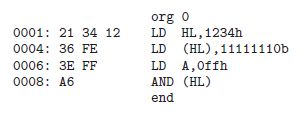

گ}1.5.1A LD r,(HL)

|

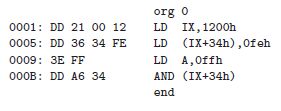

گ}1.5.1B LD r,(IX+d)

|

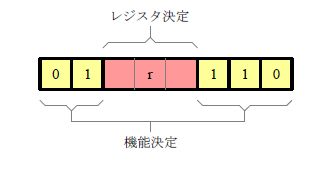

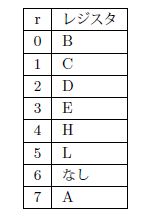

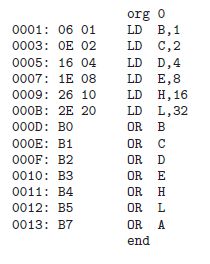

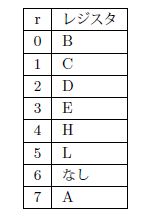

r ‚ج0پ`7 ‚ح •\1.5.1A ‚جƒŒƒWƒXƒ^‚ةٹ„‚è“–‚ؤ‚ç‚ê‚ؤ‚¢‚ـ‚·8080 ‚إ‚حژه‚ةƒŒ

ƒWƒXƒ^HL ‚ھƒپƒ‚ƒٹ”ش’n‚ًژw’è‚·‚éƒCƒ“ƒfƒbƒNƒXƒŒƒWƒXƒ^‚ةژg‚ي‚ê‚ؤ‚¢‚ـ

‚µ‚½‚ھZ80 ‚إ‚حƒŒƒWƒXƒ^IX,IY ‚ھ’ا‰ء‚³‚ꂽ‚ج‚إ’ا‰ء‚³‚ꂽƒŒƒWƒXƒ^‚ً

ژg‚¤“¯‚¶‹@”\‚ج–½—ك‚ج‚½‚ك‚ة8080 ‚جŒ³‚ج–½—ك‚ًٹg’£‚·‚éŒ`‚إ‚جگV‚½‚ب–½

—ك•„‚ج’ا‰ء‚ھ‚ب‚³‚ê‚ؤ‚¢‚ـ‚·پB

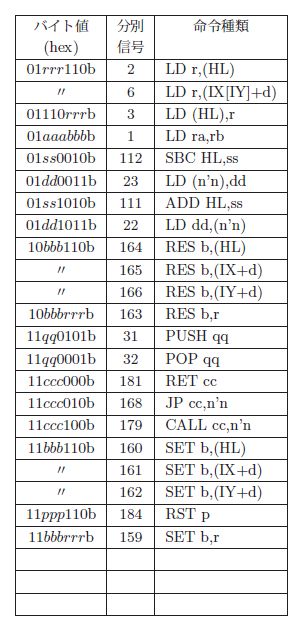

•\1.5.1A ƒŒƒWƒXƒ^ٹ„‚è“–‚ؤ

|

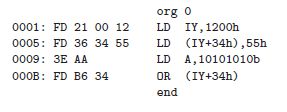

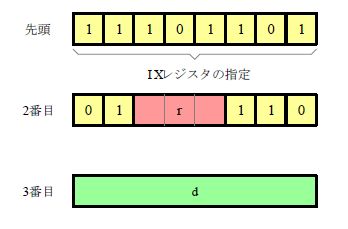

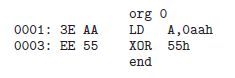

—ل‚¦‚خLD r,(HL) ‚ج“¯‚¶“‚«‚جZ80 ‚إ’ا‰ء‚³‚ꂽ–½—ك‚حLD r,(IX+d)

‚ب‚ا‚إ‚·‚ھ–½—ك•„‚ج گ}1.5.1B ‚ًŒ©”ن‚ׂé‚ئ2 ”ش–ع‚ج–½—ك•„‚حLD r,(HL) ‚ئ

“¯‚¶‚إ‚·ƒŒƒWƒXƒ^IX ‚جژw’è‚ج‚½‚ك‚ةگو“ھ‚ة–½—ك•„‚ھ•t‚¯‚ç‚ê‚ؤ‚¢‚ـ‚·پB

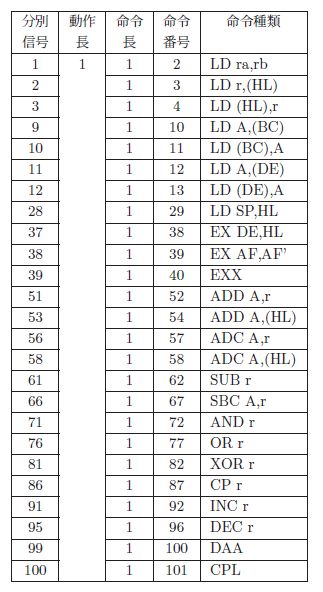

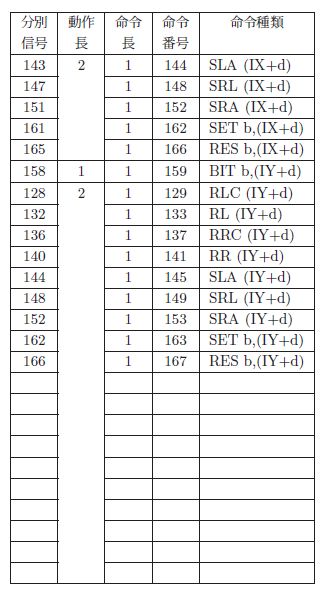

•\1.5.2A ’ا‰ء1 ’i–ع•ھ•ت

|

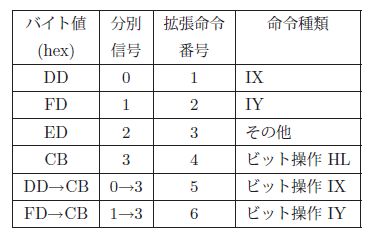

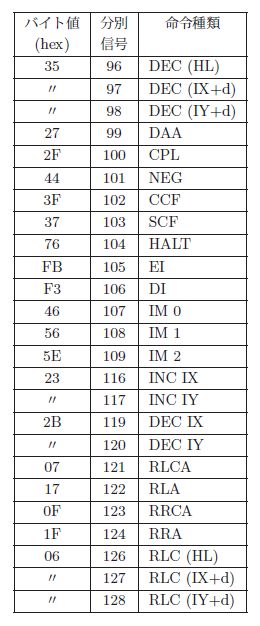

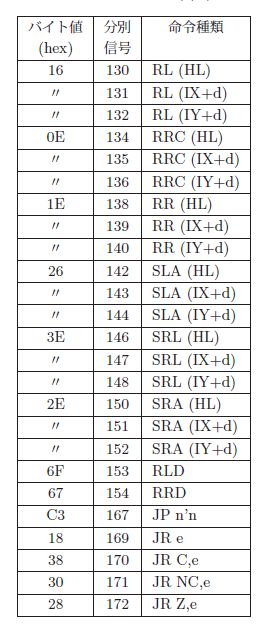

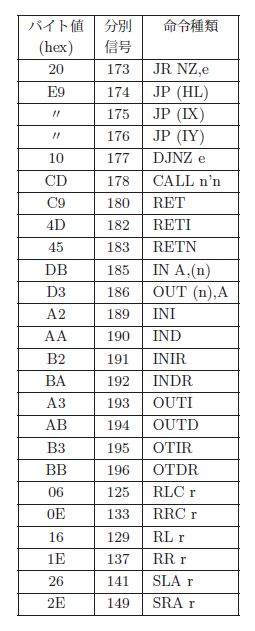

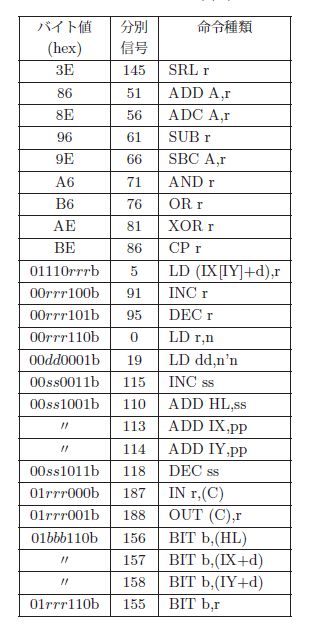

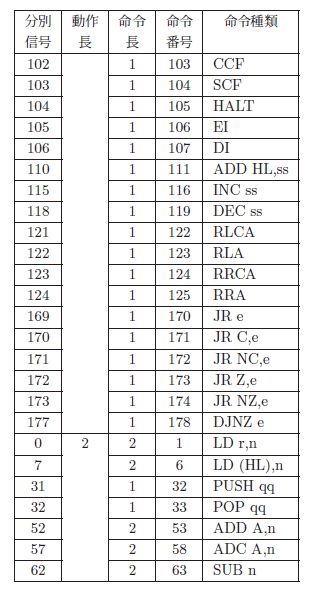

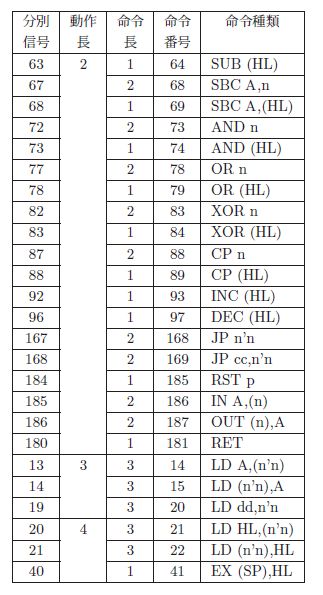

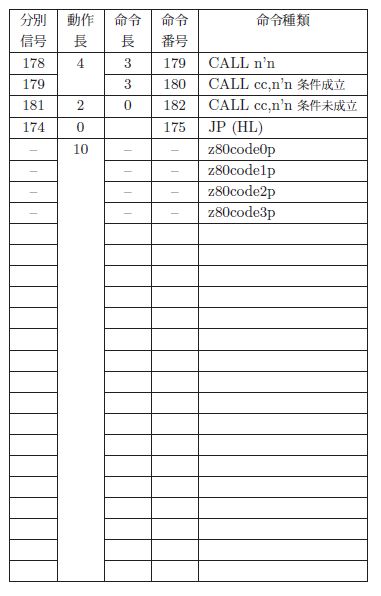

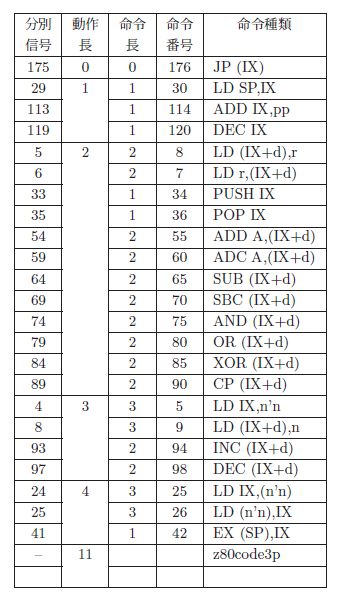

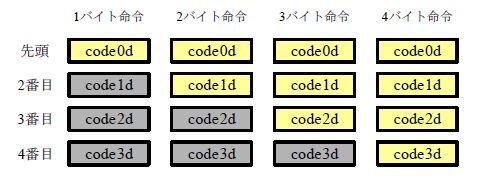

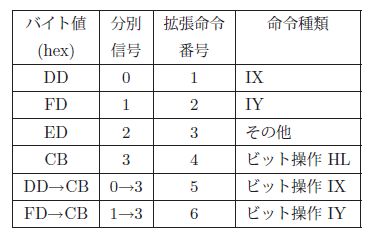

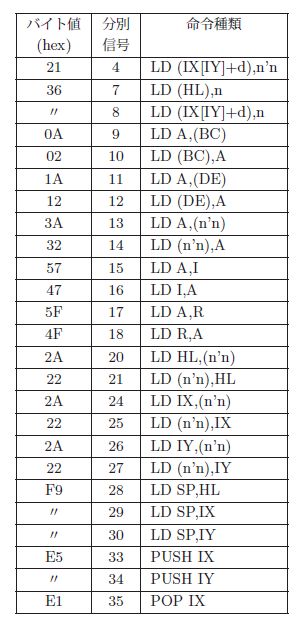

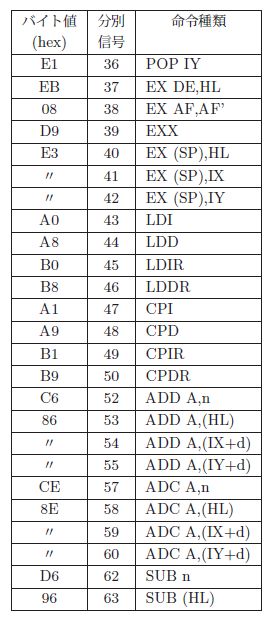

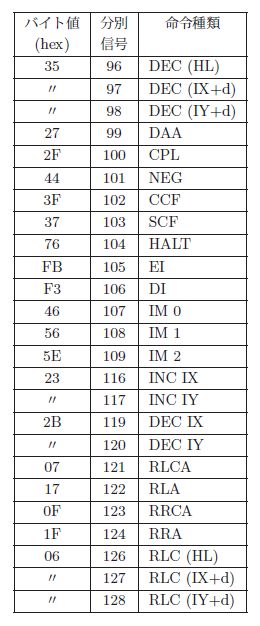

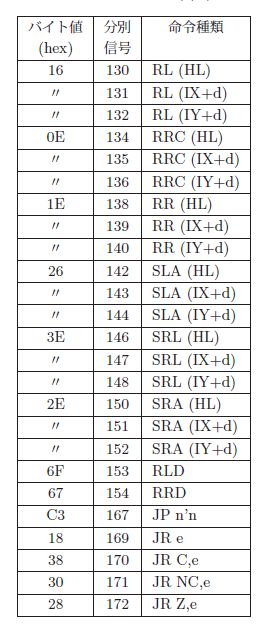

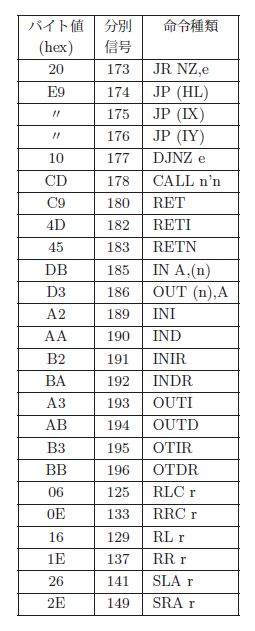

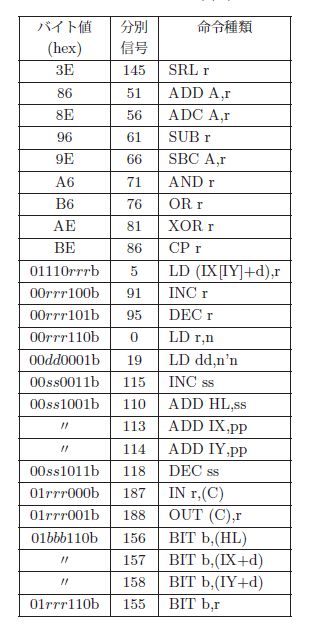

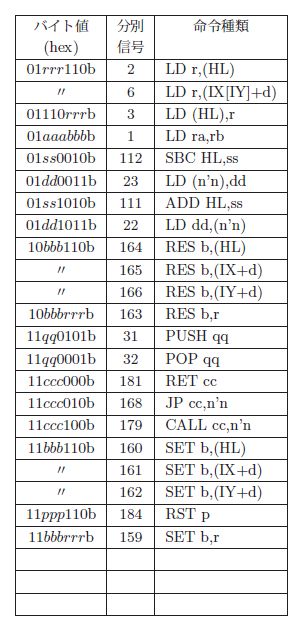

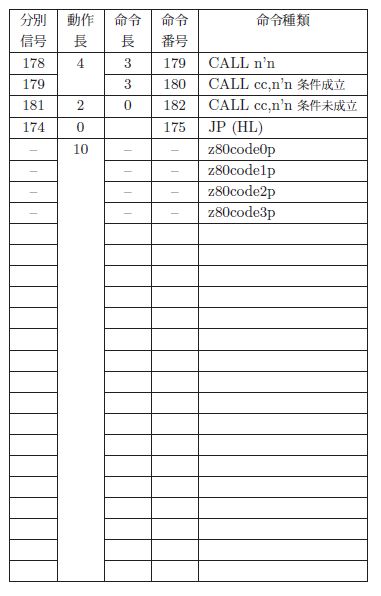

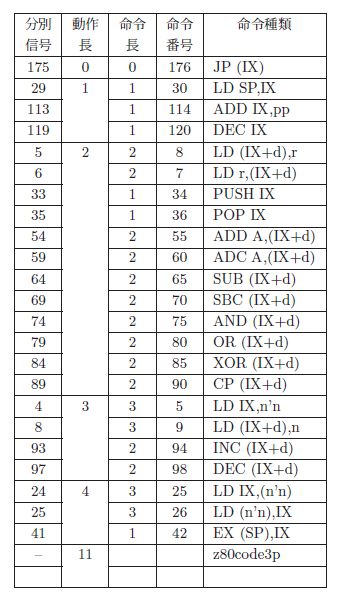

Z80 ‚ج–½—ك‚ح8080 ‚ج–½—ك‚ئ’ا‰ء‚µ‚½–½—ك‚©‚ç‚ب‚è‚ـ‚·گو“ھ‚جƒoƒCƒg‚ھ

’ا‰ء‚µ‚½–½—ك‚إ‚ ‚邱‚ئ‚ًژ¦‚·‚ج‚ھ •\1.5.2A ‚جDDh,FDh,EDh,CBh ‚ج4 Œآ

‚ج’l‚إ‚·‚±‚جڈêچ‡‚حژں‚جƒoƒCƒg‚©‚ç‹@”\‚ًژ¦‚·–½—ك‚جژي—ق‚ً•ھ•ت‚µ‚ـ‚·پB

•\1.5.2A ‚ج•ھ•تگMچ†‚جگ”’l‚ح z80code پ p ‚جپ ‚ج•”•ھ‚ة“–‚ؤ‚ؤگMچ†–¼‚ة‚ب‚è‚ـ‚·پBZ80 ‚إ‚ح–½—ك‚ج“ء’è‚ح•\1.2

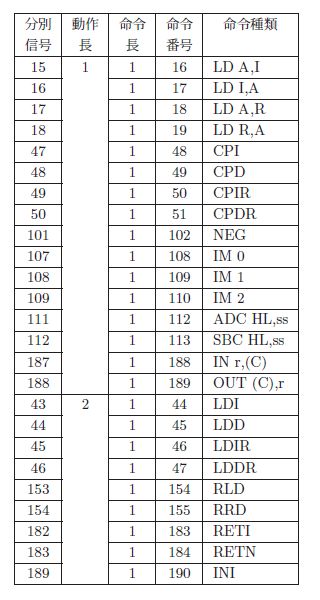

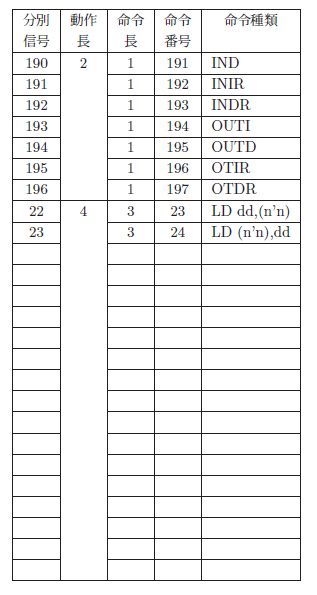

‚جگو“ھ‚جٹg’£’ا‰ء–½—ك•„‚ج‚ئ‚«‚ح2 ”ش–ع‚ج–½—ك•„‚إ‚»‚êˆبٹO‚إ‚ح1 ”ش–ع‚ج–½—ك•„‚إچs‚¦‚ـ‚·پB‹@”\‚ًژ¦‚·–½—ك

‚ج•ھ•ت‚ً •\1.5.2B ‚©‚ç •\1.5.2J ‚ةژ¦‚µ‚ـ‚·پB•\’†‚ج•ھ•تگMچ†‚جگ”’l‚ح ancode پ p ‚جپ ‚ج•”•ھ‚ة“–‚ؤ‚ؤگMچ†–¼‚ة‚ب

‚è‚ـ‚·پB

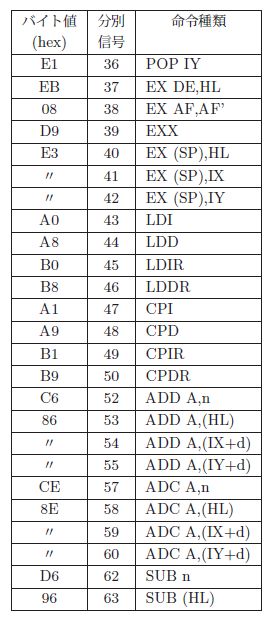

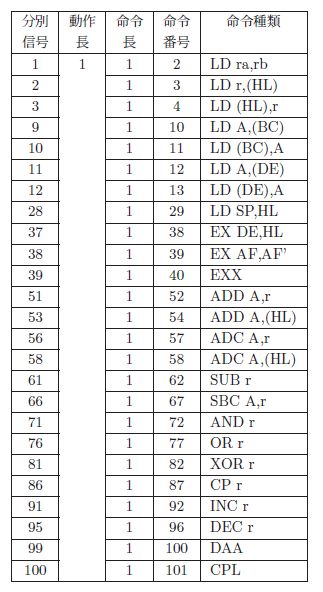

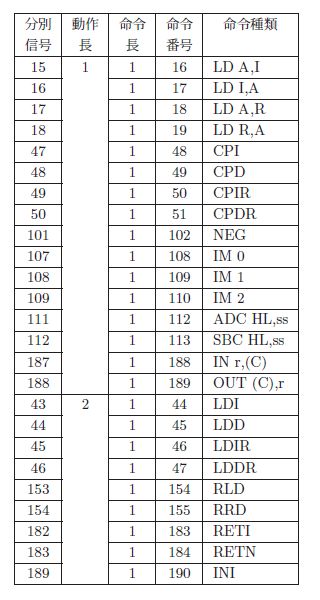

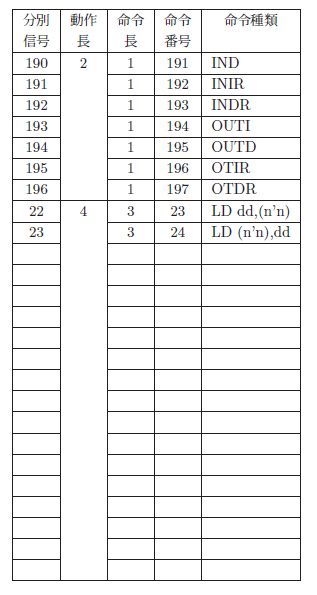

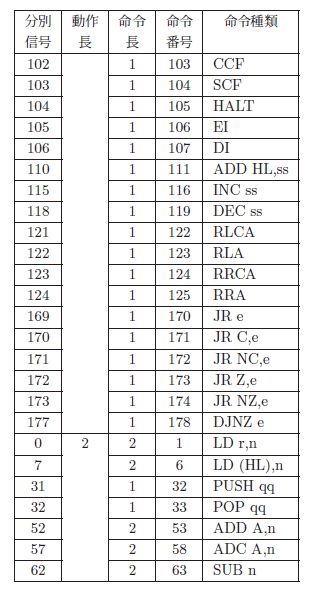

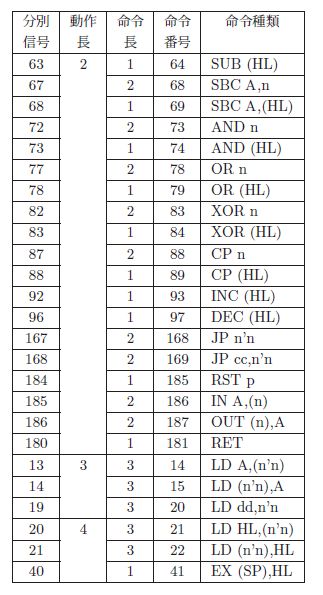

•\1.5.2B 1 ’i–ع•ھ•ت(1/8)

|

•\1.5.2C 1 ’i–ع•ھ•ت(2/8)

|

•\1.5.2D 1 ’i–ع•ھ•ت(3/8)

|

•\1.5.2E 1 ’i–ع•ھ•ت(4/8)

|

•\1.5.2F 1 ’i–ع•ھ•ت(5/8)

|

•\1.5.2G 1 ’i–ع•ھ•ت(6/8)

|

•\1.5.2H 1 ’i–ع•ھ•ت(7/8)

|

•\1.5.2J 1 ’i–ع•ھ•ت(8/8)

|

–½—ك‚ج“ء’è‚ئ‚ح‰½‚à–½—ك‚ھژہچs‚³‚ê‚ؤ‚¢‚ب‚¢‚ئ‚«‚ة–½—ك‚ًŒںڈo‚µ‚ؤ“®چى’·‚ئ–½—ك’·‚ئ–½—ك”شچ†‚ًŒˆ’è‚·‚邱

‚ئ‚ًŒ¾‚¢‚ـ‚·پB“®چى’·‚ح–½—ك‚ًژہچs‚µ‚ؤ‚¢‚éژٹش‚ً•\‚µCLK گ”‚إژ¦‚µ‚ـ‚·–½—ك’·‚ح–½—ك•„‚ج’·‚³‚إ“ا‚فژو‚è‚ج

CLK گ”‚إژ¦‚µ‚ـ‚·–½—ك”شچ†‚حŒںڈo‚µ‚½–½—ك‚جژي—ق‚ً”شچ†‚إژ¦‚µ‚ـ‚·–½—ك‚ج‹@”\‚جژہچs‚ةگو—§‚ء‚ؤ–½—ك•„‚ج’·‚³

–½—ك‚جژہچsژٹش‚â–½—ك‚جژي—ق‚ًچإڈ‰‚ة“ء’è‚·‚é•K—v‚ھ‚ ‚è‚ـ‚·پB

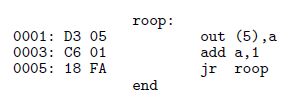

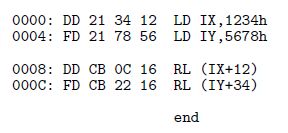

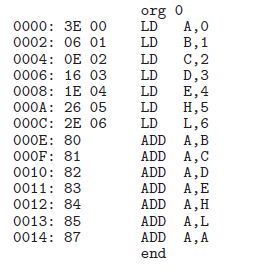

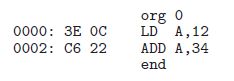

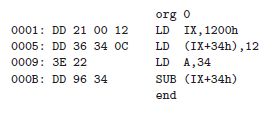

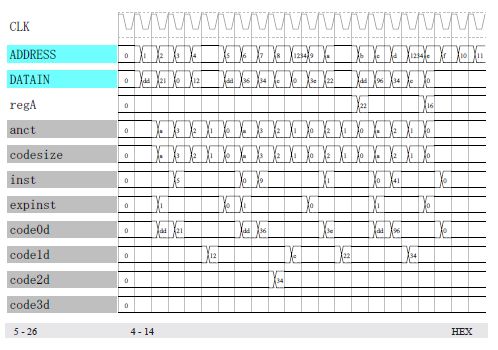

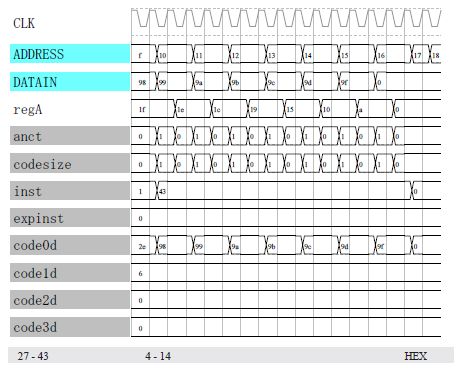

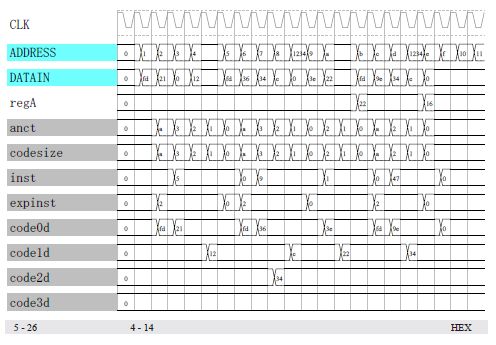

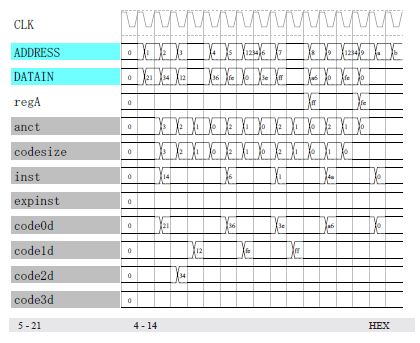

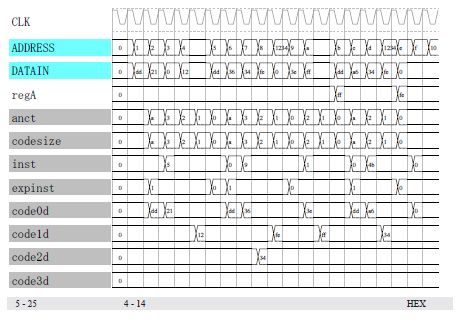

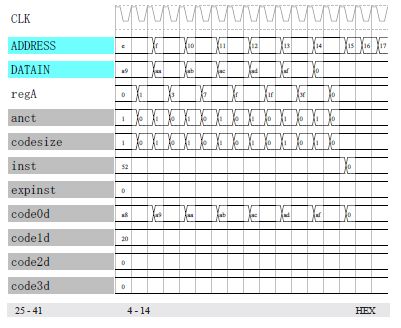

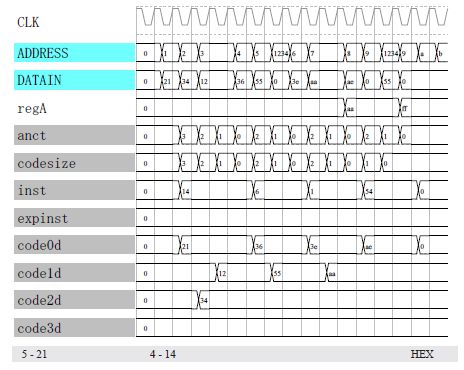

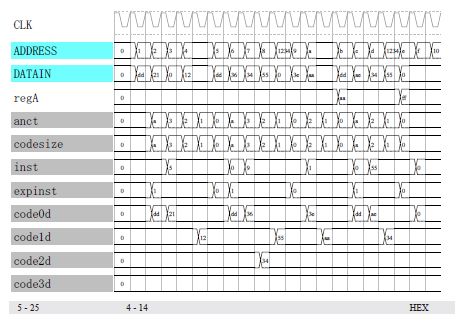

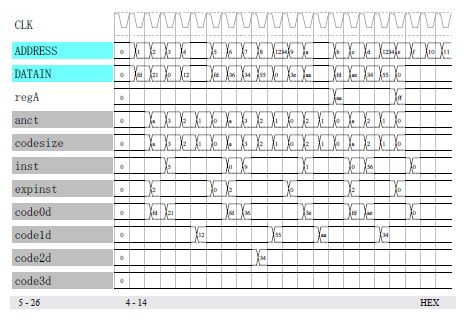

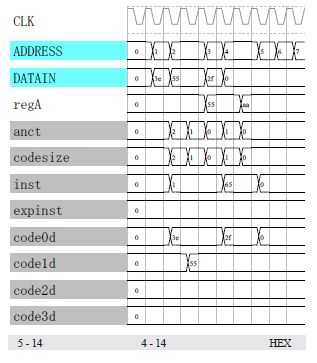

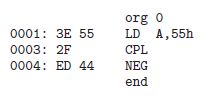

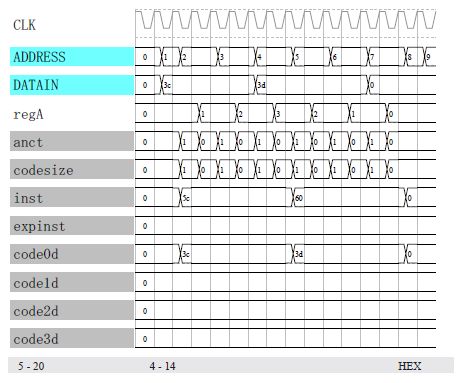

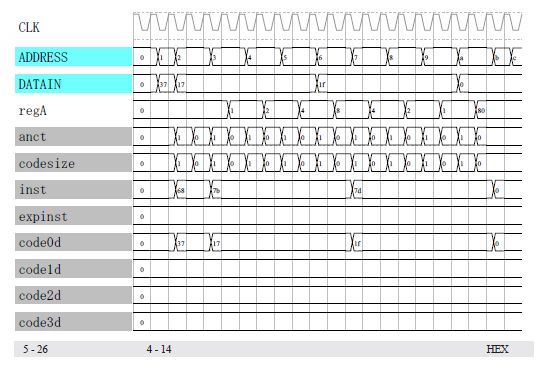

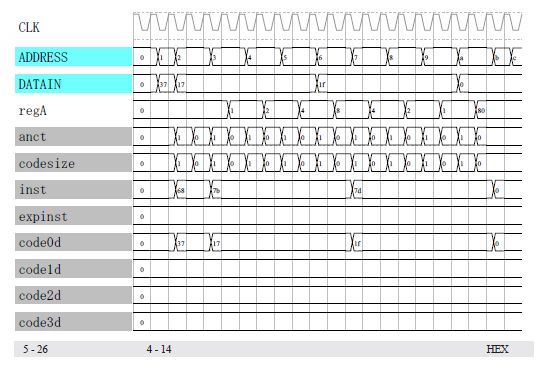

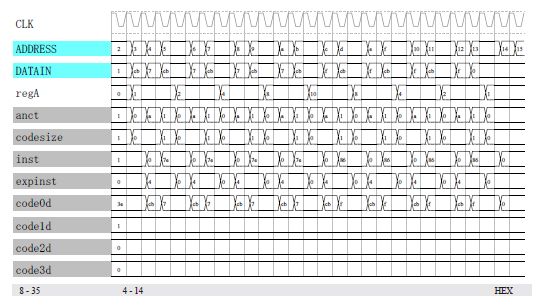

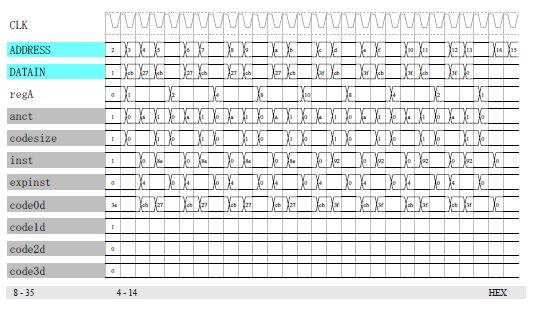

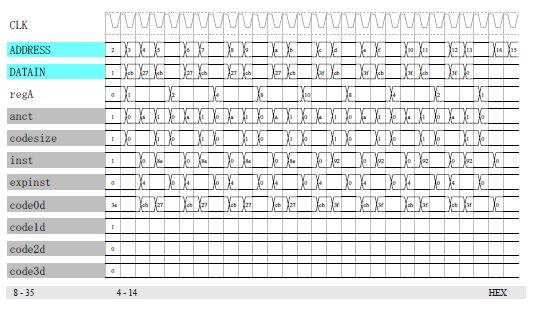

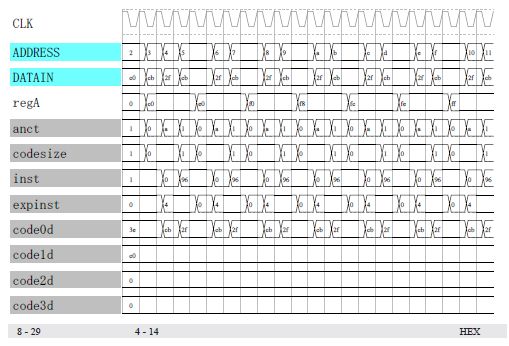

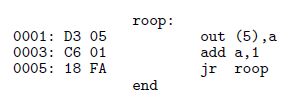

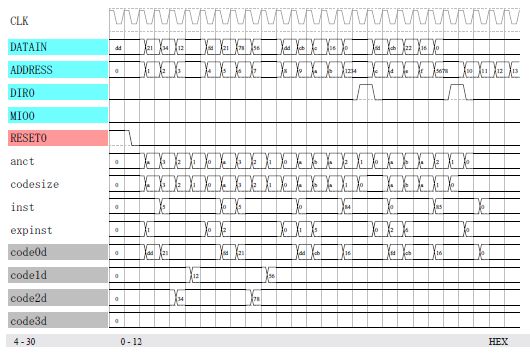

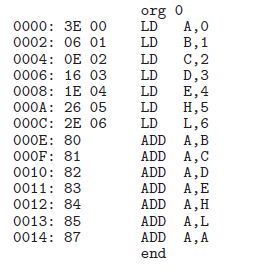

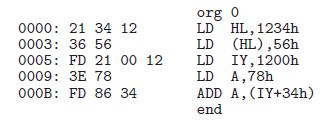

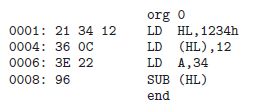

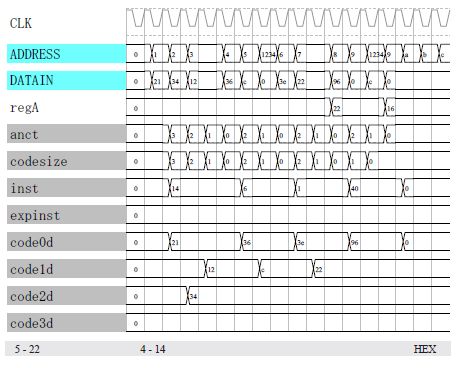

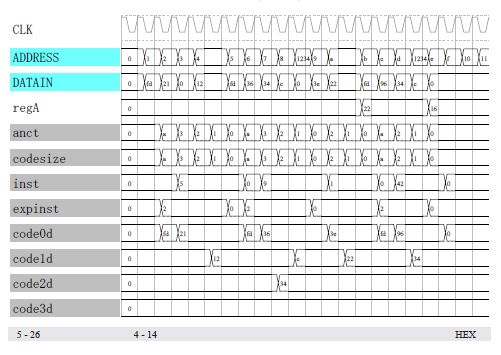

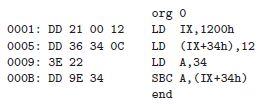

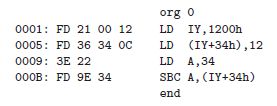

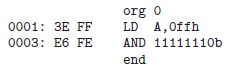

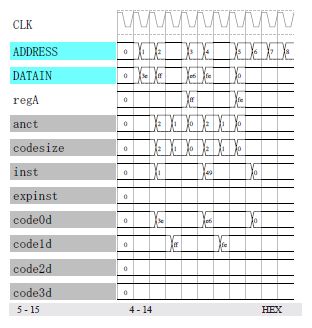

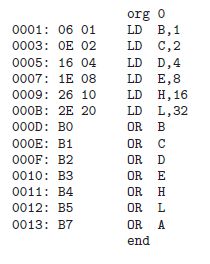

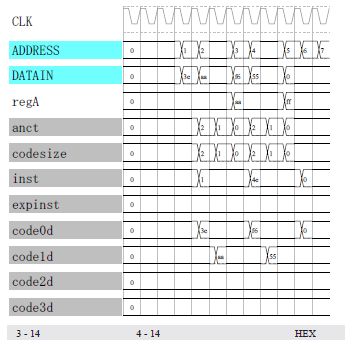

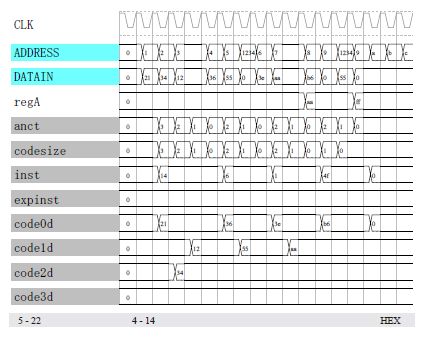

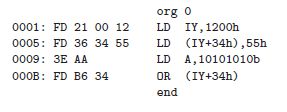

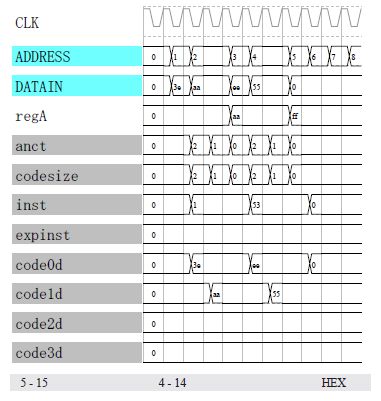

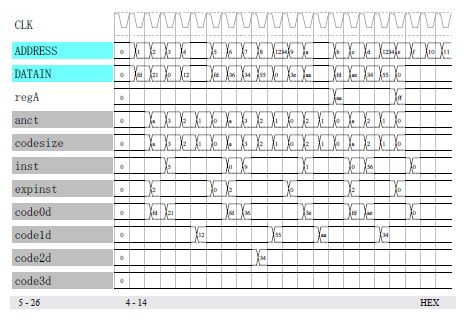

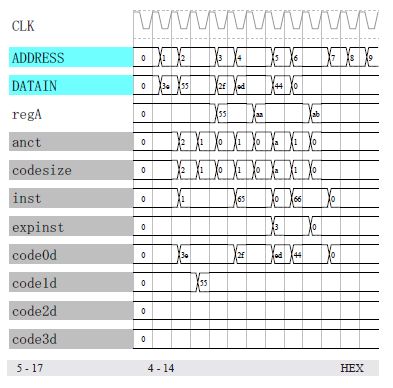

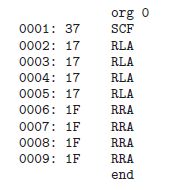

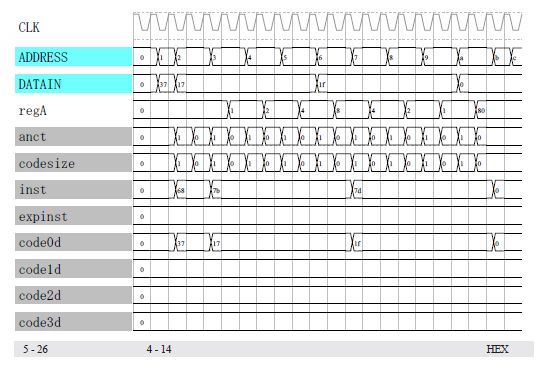

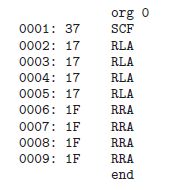

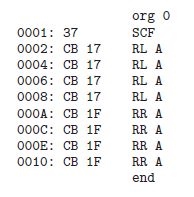

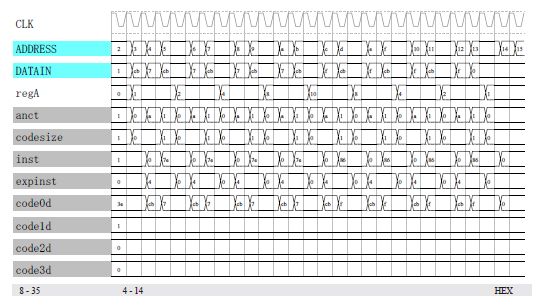

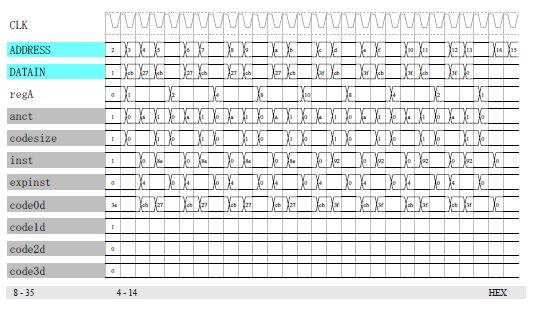

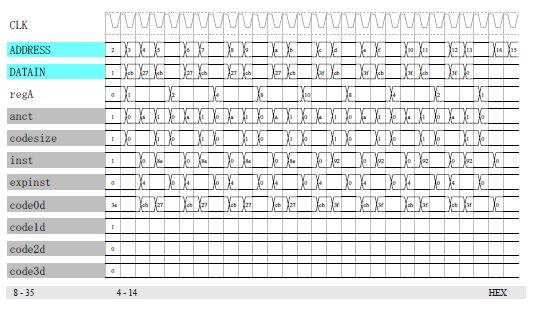

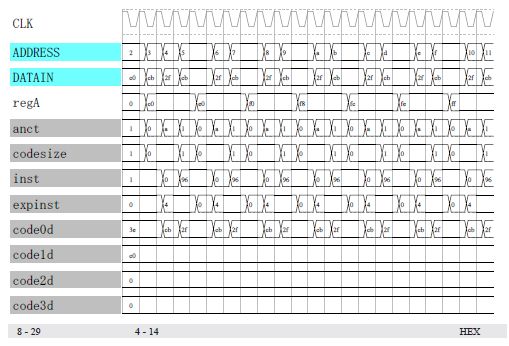

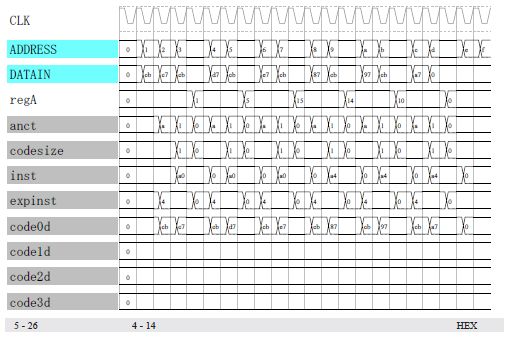

ƒٹƒXƒg1.6A ƒvƒچƒOƒ‰ƒ€a

|

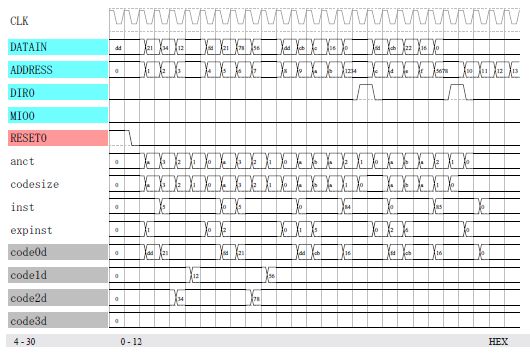

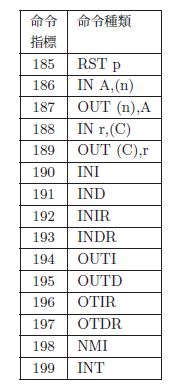

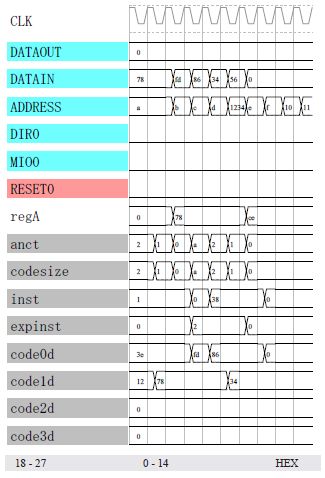

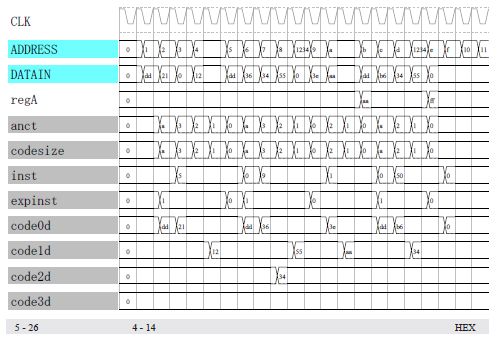

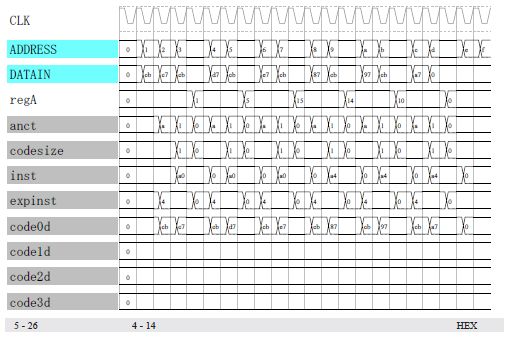

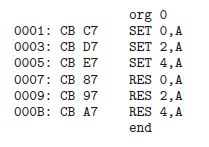

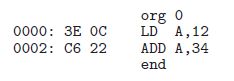

ƒٹƒXƒg1.6A ‚جƒvƒچƒOƒ‰ƒ€‚ً—ل‚ة‚µ‚ؤگà–¾‚µ‚ـ‚·پBOUT (n),A ‚ح

2 ƒoƒCƒg‚ج–½—ك•„‚ب‚ج‚إ–½—ك’·‚ح2 ‚ة‚ب‚è‚ـ‚·“®چى’·‚ح2 ‚ة

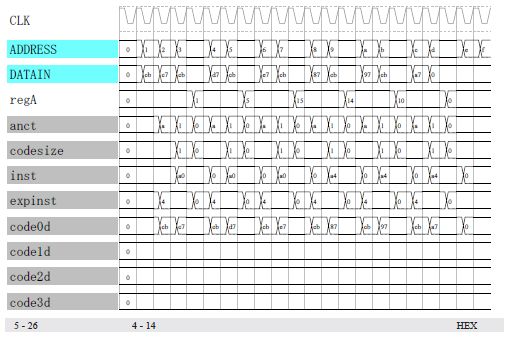

‚ب‚è‚ـ‚·–½—ك”شچ†‚ح187 ‚ة‚ب‚è‚ـ‚·–½—ك‚ج“ء’è“_‚ح گ}1.6A ‚ج

anct ‚ھ0 ‚©‚ç2 ‚ة‚ب‚ء‚½‚ئ‚±‚ë‚إ‚·ٹe–½—ك‚ج“®چى’·پA–½—ك’·پA

–½—ك”شچ†‚ح •\1.6A ‚©‚ç •\1.6K ‚ةژ¦‚µ‚ـ‚·پB

ƒٹƒXƒg1.6A ƒvƒچƒOƒ‰ƒ€“®چىa

|

•\1.6A –½—ك“ء’è(1/10)

|

•\1.6B –½—ك“ء’è(2/10)

|

•\1.6C –½—ك“ء’è(3/10)

|

•\1.6D –½—ك“ء’è(4/10)

|

•\1.6E –½—ك“ء’è(5/10)

|

•\1.6F –½—ك“ء’è(6/10)

|

•\1.6G –½—ك“ء’è(7/10)

|

•\1.6H –½—ك“ء’è(8/10)

|

•\1.6J –½—ك“ء’è(9/10)

|

•\1.6K –½—ك“ء’è(10/10)

|

- ’تڈي–½—ك

گو“ھ‚ةٹg’£–½—ك•„‚ً•t‚¯‚ب‚¢–½—ك‚إ‚·8080 ‚ج–½—ك‚ھژه‚إ‚·‚ھZ80 ‚إ’ا‰ء‚³‚ꂽ–½—ك‚àٹـ‚ٌ‚إ‚¢‚ـ‚·

•\1.6A ‚©‚ç •\1.6D ‚إ‚·پB

- ٹg’£–½—ك1

ƒŒƒWƒXƒ^IX ‚ًژg‚¤–½—كŒQ‚إ‚· •\1.6E ‚إ‚·پB

-

ٹg’£–½—ك2

ƒŒƒWƒXƒ^IY ‚ًژg‚¤–½—كŒQ‚إ‚· •\1.6F ‚إ‚·پB

-

ٹg’£–½—ك3

گو“ھ‚ج–½—ك•„‚ھEDh ‚إژn‚ـ‚é–½—كŒQ‚إ‚· •\1.6G ‚©‚ç •\1.6H ‚إ‚·پB

-

ٹg’£–½—ك4

Z80 ‚إ’ا‰ء‚³‚ꂽƒrƒbƒg‘€چى–½—ك‚إ‚· •\1.6J ‚©‚ç •\1.6K ‚إ‚·پB

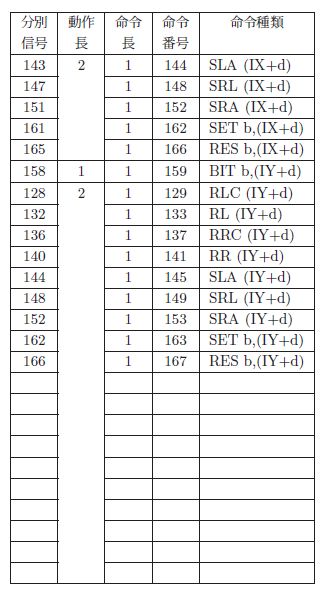

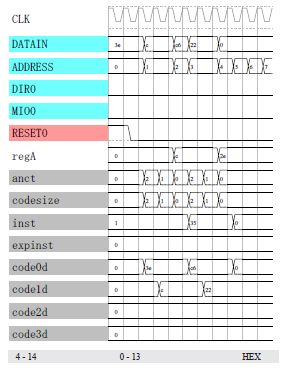

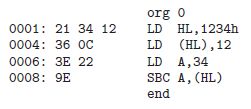

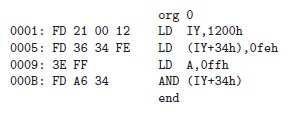

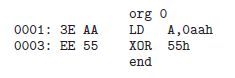

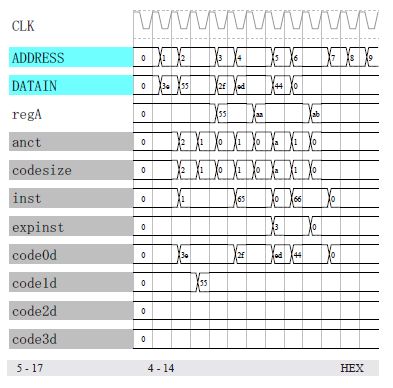

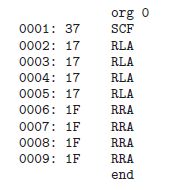

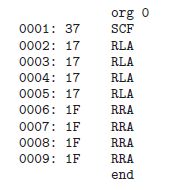

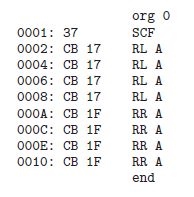

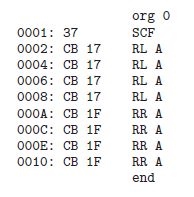

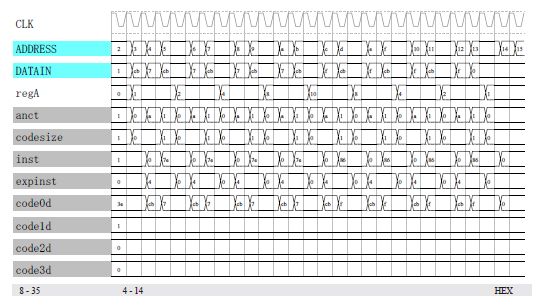

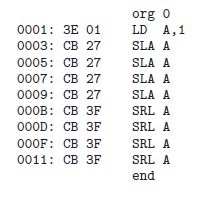

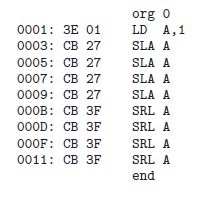

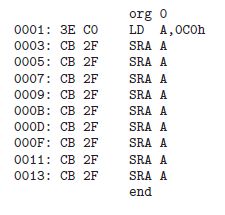

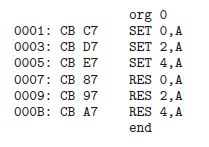

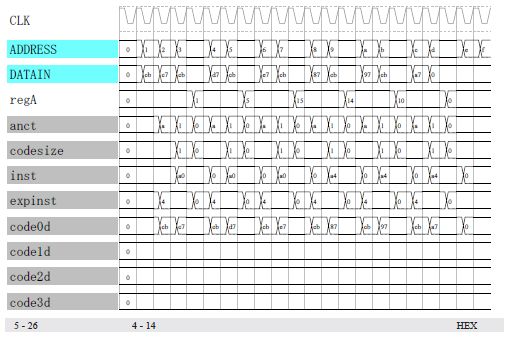

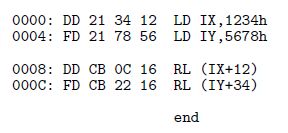

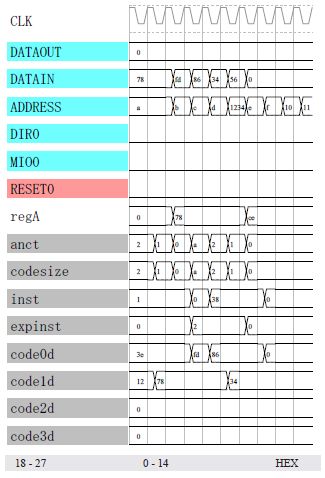

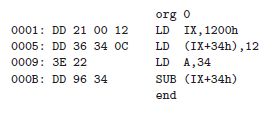

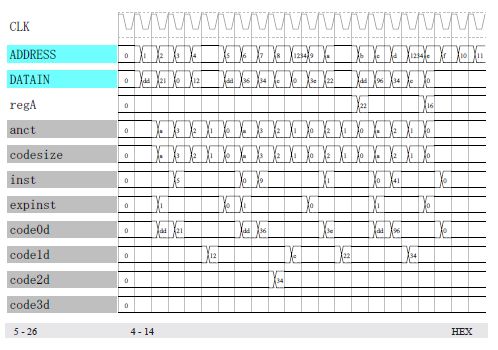

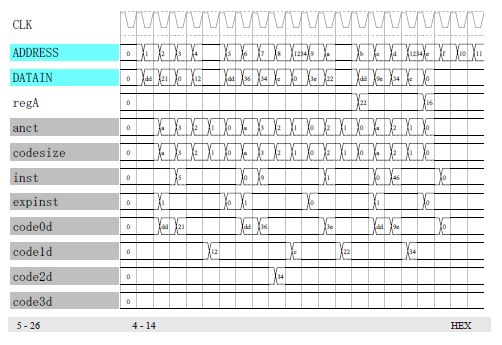

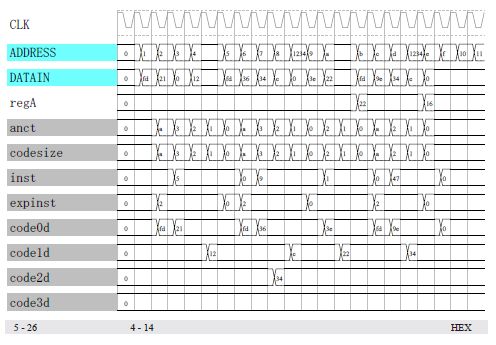

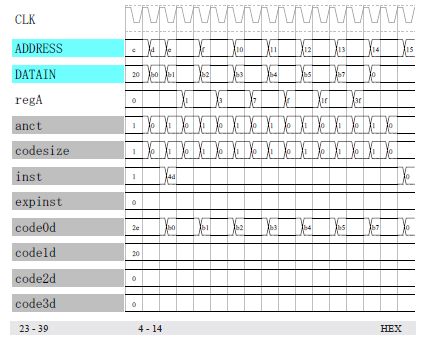

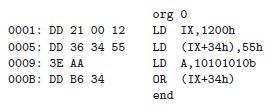

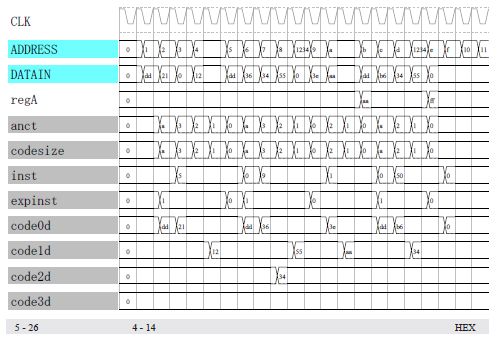

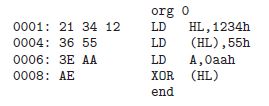

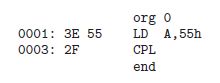

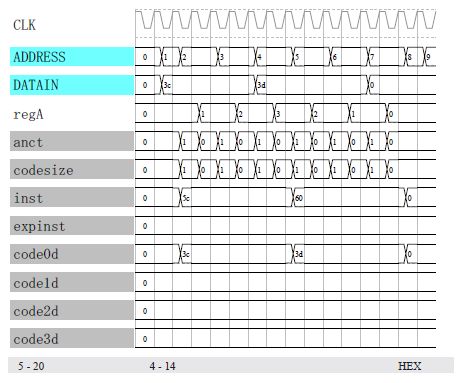

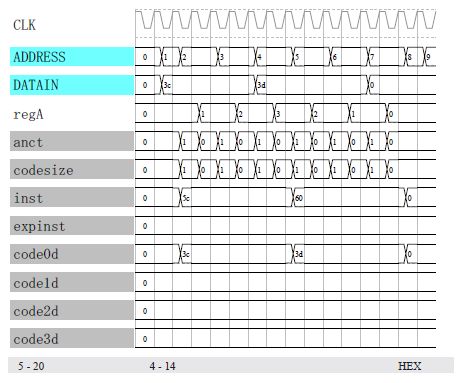

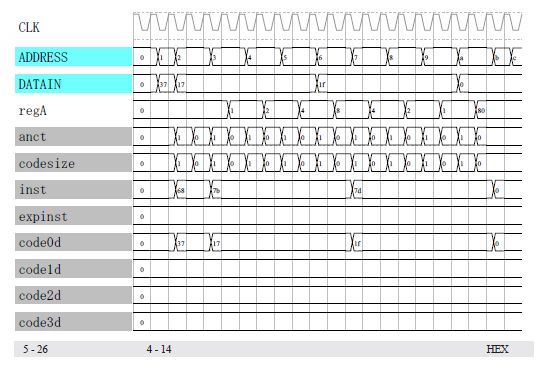

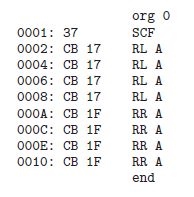

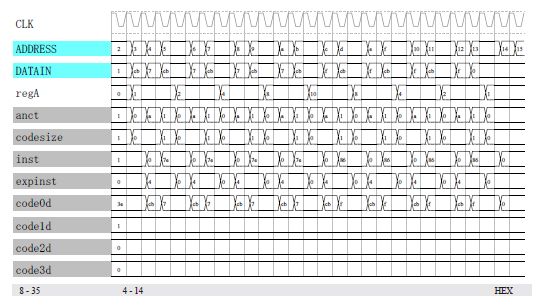

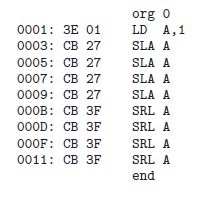

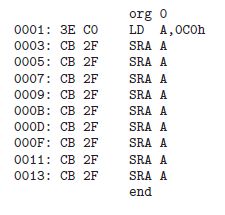

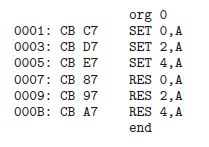

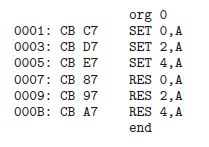

ƒٹƒXƒg1.6.1A ƒvƒچƒOƒ‰ƒ€b

|

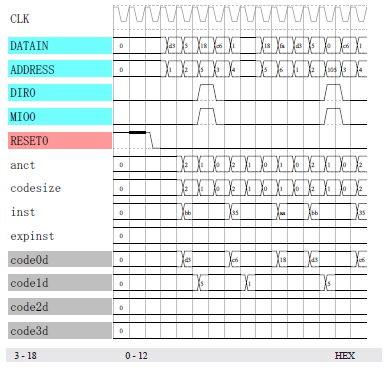

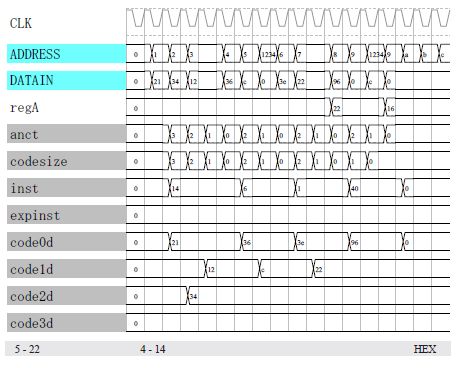

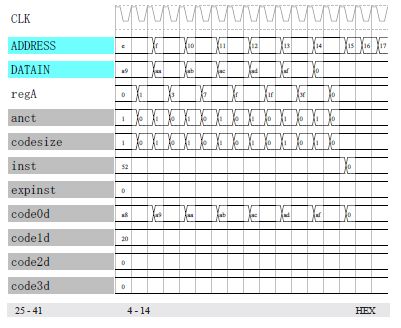

–½—ك•„‚جŒ`‘ش‚إ3 ژي—ق‚جچs’ِ‚ھ‚ ‚è‚ـ‚·گو“ھ‚ة •\1.5.2A ‚ج‚و‚¤

‚بٹg’£‚ج–½—ك•„‚ج‚ب‚¢ڈêچ‡‚ئ1 Œآ‚ ‚éڈêچ‡‚ئ2 Œآ‚ ‚éڈêچ‡‚ج3

ژي—ق‚إ‚·پB–½—ك‚ج‘ه•ھ—ق‚إ‚ح7 ژي—ق‚ة•ھ‚¯‚ç‚ê‚ـ‚·گو“ھ‚ةٹg’£

–½—ك•„‚ج‚ب‚¢–½—ك‚ھ1 ژي—قپAگو“ھ‚ة1 Œآ‚جٹg’£–½—ك•„‚ھ‚ ‚éڈê

چ‡‚ھ4 ژي—قپAگو“ھ‚ة2 Œآ‚جٹg’£–½—ك•„‚ھ‚ ‚éڈêچ‡‚جŒv7 ژي—ق‚إ

‚·‚±‚ê‚ç‚حexpinst ‚ةژ¦‚µ‚ـ‚·پBٹg’£–½—ك•„‚إ‚ح–½—ك‚ج“ء’è‚ھ

‚إ‚«‚ب‚¢‚ج‚إ“ء’è‚إ‚«‚é–½—ك‚ـ‚إ“ا‚فگi‚ق•K—v‚ھ‚ ‚è‚ـ‚·‚ھ‚»

‚جٹش‚ح“®چى’·‚ئ–½—ك’·‚ح‰¼‚ج’l‚ج10 ‚ً‹L‰¯‚µ‚ؤ‚¨‚«‚ـ‚·ٹg’£–½—ك•„‚ھ2 Œآ‚ ‚éڈêچ‡‚ح10پ¨11 ‚ئ‚µ‚ـ‚·ژہŒّ–½

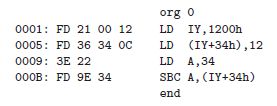

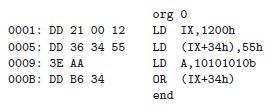

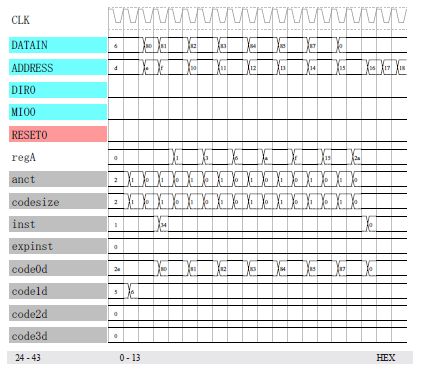

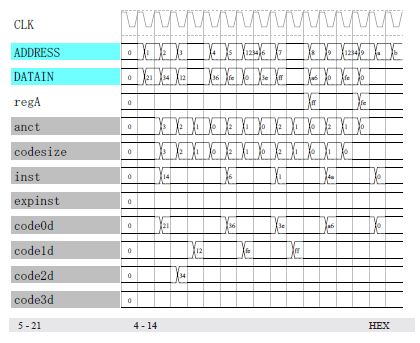

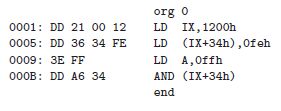

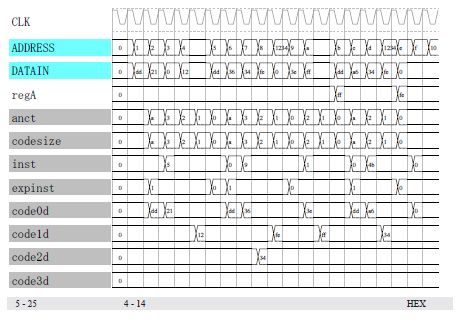

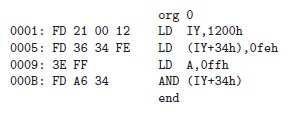

—ك•„‚ً“ا‚ٌ‚¾‚ئ‚«‚ةگ³‹K‚ج’l‚ً‹L‰¯‚µ‚ـ‚·پBٹg’£–½—ك•„‚ج‚ ‚éƒvƒچƒOƒ‰ƒ€‚ً ƒٹƒXƒg1.6.1A ‚ة‚»‚ج“®‚«‚ً گ}1.6.1A ‚ةژ¦‚µ

‚ـ‚·پB

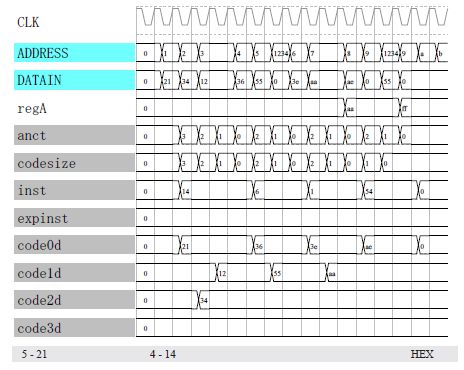

گ}1.6.1A ƒvƒچƒOƒ‰ƒ€“®چىb

|

“®چى’·‚ح–½—ك‚ج‘Sچs’ِ‚ً

–ش—…‚·‚é‚à‚ج‚إ–½—ك‚جژہچs‚ة•K—v‚بCLK گ”‚إژ¦‚µ‚ـ‚·‚ھچإ’Z‚إ‚à–½—ك’·ˆبڈم‚ة‚ب‚è

‚ـ‚·“®چى’·‚ح–½—ك‚ج“ء’è“_‚إ‹L‰¯‚³‚ê‚ؤCLK ‚إ گ}1.6A ‚ج‚و‚¤‚ةڈ‡ژںŒ¸گ”‚³‚ê‚ؤ‚¢‚«‚ـ‚·0 ‚ة‚ب‚ء‚½‚ئ‚«‚ح–½—ك

‚جژہچs‚ًڈI—¹‚µ‚ؤ‚¢‚ـ‚·پB

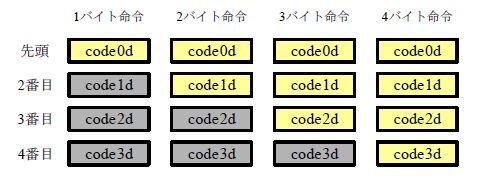

–½—ك‚جژي—ق‚ة‚و‚ء‚ؤ’·‚³‚حˆظ‚ب‚èچإ‘ه‚إ4 ƒoƒCƒg‚ة‚ب‚è‚ـ‚·–½—ك’·‚ح–½—ك‚ج“ء’è“_‚إ‹L‰¯‚³‚ê‚ؤCLK ‚إ

گ}1.6A ‚ج‚و‚¤‚ةڈ‡ژںŒ¸گ”‚³‚ê‚ؤ‚¢‚«‚ـ‚·0 ‚ة‚ب‚ء‚½‚ئ‚«‚ح–½—ك‚ج“ا‚فژو‚è

‚حڈI—¹‚µ‚ؤ‚¢‚ـ‚·–½—ك•„‚ح–½—ك’·‚ة‚و‚ء‚ؤ گ}1.6.3A ‚ج‚و‚¤‚ة“ا‚فژو‚ç‚ê‚ـ‚·پB

گ}1.6.3A –½—ك“ا‚فژو‚è

|

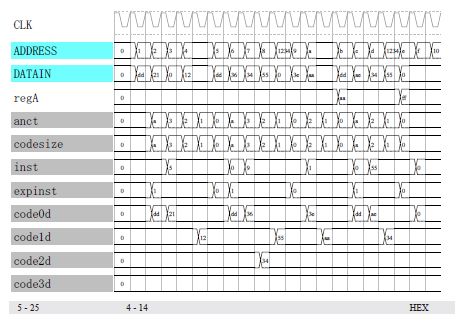

–½—ك‚جژي—ق‚ح–½—ك”شچ†‚جinst ‚ة‹L‰¯‚µ‚ـ‚·–½—ك‚ج‹@”\‚جژہچs‚ح–½—ك”شچ†‚ة‘خ‰‚µ‚½

گ}1.6.4A ‚©‚ç گ}1.6.4B ‚ج–½

—كژw•W‚جinstp ‚ئcode0d ‚©‚çcode3d ‚ة‹L‰¯‚µ‚½–½—ك•„‚©‚ç‘I‚رڈo‚³‚ê‚ـ‚·پB

•\1.6.4A –½—كژw•W(1/2)

|

•\1.6.4B –½—كژw•W(2/2)

|

–½—ك‚ج“ء’è‚ة‚و‚ء‚ؤژي—ق‚ئژہچsژٹش‚ھ•ھ‚©‚ء‚½Œم‚حCLK گ”‚إژ¦‚³‚ꂽژہچsژٹش‚ح–½—ك‚ج“ء’èژ‚ة‹L‰¯‚³‚ꂽ

’l‚©‚çڈ‡ژںŒ¸گ”‚³‚ê‚ؤ‚¢‚«‚ـ‚·–½—ك‚جژي—ق‚ج instp. پ ‚ئژہچsژٹش‚جanct ‚ًڈئچ‡‚·‚邱‚ئ‚إ‚»‚ج–½—ك‚جژŒn

—ٌ‚جٹeˆت’u‚جڈˆ—‚ًŒˆ’肵‚ؤژہچs‚µژہچsژٹش‚جڈI—¹ژ‚ة‚ح–½—ك‚ج‹@”\‚ً’B‚µ‚ـ‚·ڈˆ—‚ئ‚حژں‚ج‚à‚ج‚ھ‚ ‚è‚ـ‚·پB

- ƒŒƒWƒXƒ^‚ج“ا‚فڈ‘‚«

- ƒtƒ‰ƒO‚ج“ا‚فڈ‘‚«

- ƒپƒ‚ƒٹ‚ج“ا‚فڈ‘‚«

- ‰‰ژZ

- ƒAƒhƒŒƒX’[ژq‘€چى

- ƒfپ[ƒ^’[ژq‘€چى

‚±‚ê‚ç‚ًڈ‡”ش‚ة‚ ‚é‚¢‚ح•ہچs‚µ‚ؤچs‚¢‚ـ‚·پB

‰‰ژZ‚ح3 ژي—ق‚ج‰‰ژZٹي‚إڈW–ٌ‚µ‚ؤچs‚¢‚ـ‚·3 ژي—ق‚ج‰‰ژZٹي‚حƒrƒbƒgگ”‚إ•ھ‚¯‚ؤ‚ ‚è4 ƒrƒbƒgپA8 ƒrƒbƒgپA16

ƒrƒbƒg‚ھ‚ ‚è‚ـ‚·پB

‚ا‚ج‰‰ژZٹي‚àٹî–{‚جچ\‘¢‚ح“¯‚¶‚إ‚·‚ھ“ü—ح•”پA‰‰ژZ•”پAڈo—ح•”‚ج3 Œآ‚ج•”•ھ‚©‚çچ\گ¬‚µ‚ـ‚·پB‰‰ژZ•”‚ح•K—v‚ب

‰‰ژZ‚جگ”‚¾‚¯‚ ‚è‚ـ‚·a ‚ئb ‚ج2 Œآ‚ج“ü—ح•”‚ئ1 Œآ‚جڈo—ح•”‚ح‘I‘ًٹي‚ة‚ب‚ء‚ؤ‚¢‚ؤ–½—ك‚جژي—ق‚ة‚و‚ء‚ؤ‘I‘ً‚µ

‚½’l‚ً‰‰ژZ•”‚ة“ü—ح‚µ‚ؤ‘I‘ً‚µ‚½‰‰ژZ•”‚ج‰‰ژZ’l‚ًڈo—ح‚µ‚ـ‚·پB

2 گi‰»10 گiگ”‚جŒvژZ‚ة‚و‚éƒtƒ‰ƒOH ‚ً•د‰»‚³‚¹‚邽‚ك‚ة‚ ‚è‚ـ‚·‰‰ژZ•”‚ح‰ءژZپAŒ…ڈم‚°‰ءژZپAŒ¸ژZپAŒ…ژط‚è

Œ¸ژZ‚ج4 ژي—ق‚ًژ‚؟‚ـ‚·پB

- ADD A,r

- ADD A,n

- ADD A,(HL)

- ADD A,(IX+d)

- ADD A,(IY+d)

- INC r

- INC (HL)

- INC (IX+d)

- INC (IY+d)

- SUB r

- SUB n

- SUB (HL)

- SUB (IX+d)

- SUB (IY+d)

- CP r

- CP (HL)

- CP (IX+d)

- CP (IY+d)

- ADC A,r

- ADC A,n

- ADC A,(HL)

- ADC A,(IX+d)

- ADC A,(IY+d)

- SBC A,r

- SBC A,n

- SBC A,(HL)

- SBC A,(IX+d)

- ADD A,r

- ADD A,n

- ADD A,(HL)

- ADD A,(IX+d)

- ADD A,(IY+d)

- ADC A,r

- ADC A,n

- ADC A,(HL)

- ADC A,(IX+d)

- ADC A,(IY+d)

- SUB r

- SUB n

- SUB (HL)

- SUB (IX+d)

- SUB (IY+d)

- SBC A,r

- SBC A,n

- SBC A,(HL)

- SBC A,(IX+d)

- SBC A,(IY+d)

- CP r

- CP n

- CP (HL)

- CP (IX+d)

- CP (IY+d)

- NEG

- INC r

- INC (HL)

- INC (IX+d)

- INC (IY+d)

- DEC r

- DEC (HL)

- DEC (IX+d)

- DEC (IY+d)

- ADD A,r

- ADC A,r

- SUB r

- SBC A,r

- CP r

- INC r

- DEC r

- ADD A,n

- ADC A,n

- SUB n

- SBC A,n

- CP n

- ADD A,(HL)

- ADD A,(IX+d)

- ADD A,(IY+d)

- ADC A,(HL)

- ADC A,(IX+d)

- ADC A,(IY+d)

- SUB (HL)

- SUB (IX+d)

- SUB (IY+d)

- SBC A,(HL)

- SBC A,(IX+d)

- SBC A,(IY+d)

- CP (HL)

- CP (IX+d)

- CP (IY+d)

- INC (HL)

- INC (IX+d)

- INC (IY+d)

- DEC (HL)

- DEC (IX+d)

- DEC (IY+d)

NEG ‚¾‚¯‚إ‚·پB

ژZڈp‰‰ژZ‚ج‰ءژZپAŒ¸ژZپAŒ…ڈم‚°‰ءژZپAŒ…ژط‚茸ژZ‚ج4 ژي—ق‚ئک_—‰‰ژZ‚جک_—گدپAک_—کaپA”r‘¼“Iک_—کa‚ج3 ژي

—ق‚ئƒrƒbƒgˆع“®‚ج7 ژي—ق‚جŒv14 ژي—ق‚ج‰‰ژZ•”‚ًژ‚؟‚ـ‚·پB

- ADD A,r

- ADD A,n

- ADD A,(HL)

- ADD A,(IX+d)

- ADD A,(IY+d)

- INC r

- INC (HL)

- INC (IX+d)

- INC (IY+d)

- DEC r

- DEC (HL)

- DEC (IX+d)

- DEC (IY+d)

- NEG

- SUB r

- SUB n

- SUB (HL)

- SUB (IX+d)

- SUB (IY+d)

- CP r

- CP n

- CP (HL)

- CP (IX+d)

- CP (IY+d)

- INI

- IND

- INIR

- INDR

- OUTI

- OUTD

- OTIR

- OTDR

- ADC A,r

- ADC A,n

- ADC A,(HL)

- ADC A,(IX+d)

- ADC A,(IY+d)

- SBC A,r

- SBC A,n

- SBC A,(HL)

- SBC A,(IX+d)

- SBC A,(IY+d)

- AND r

- AND n

- AND (HL)

- AND (IX+d)

- AND (IY+d)

- BIT b,r

- BIT b,(HL)

- BIT b,(IX+d)

- BIT b,(IY+d)

- RES b,r

- RES b,(HL)

- RES b,(IX+d)

- RES b,(IY+d)

- OR r

- OR n

- OR (HL)

- OR (IX+d)

- OR (IY+d)

- SET b,r

- SET b,(HL)

- SET b,(IX+d)

- SET b,(IY+d)

- IN r,(C)

- XOR r

- XOR n

- XOR (HL)

- XOR (IX+d)

- XOR (IY+d)

- RLCA

- RLA

- RLC r

- RLC (HL)

- RLC (IX+d)

- RLC (IY+d)

- RL r

- RL (HL)

- RL (IX+d)

- RL (IY+d)

- RRC r

- RRC (HL)

- RRC (IX+d)

- RRC (IY+d)

- RRCA

- RRA

- RR r

- RR (HL)

- RR (IX+d)

- RR (IY+d)

- SLA r

- SLA (HL)

- SLA (IX+d)

- SLA (IY+d)

- SRL r

- SRL (HL)

- SRL (IX+d)

- SRL (IY+d)

- SRA r

- SRA (HL)

- SRA (IX+d)

- SRA (IY+d)

- ADD A,r

- ADD A,n

- ADD A,(HL)

- ADD A,(IX+d)

- ADD A,(IY+d)

- ADC A,r

- ADC A,n

- ADC A,(HL)

- ADC A,(IX+d)

- ADC A,(IY+d)

- SUB r

- SUB n

- SUB (HL)

- SUB (IX+d)

- SUB (IY+d)

- AND r

- AND n

- AND (HL)

- AND (IX+d)

- AND (IY+d)

- OR r

- OR n

- OR (HL)

- OR (IX+d)

- OR (IY+d)

- XOR r

- XOR n

- XOR (HL)

- XOR (IX+d)

- XOR (IY+d)

- CP r

- CP n

- CP (HL)

- CP (IX+d)

- CP (IY+d)

- CPL

- NEG

- RLCA

- RLA

- RRCA

- RRA

- INC r

- INC (HL)

- INC (IX+d)

- INC (IY+d)

- DEC r

- DEC (HL)

- DEC (IX+d)

- DEC (IY+d)

- RLC r

- RL r

- RRC r

- RR r

- SLA r

- SRL r

- SRA r

- BIT b,r

- SET b,r

- RES b,r

- RLC (HL)

- RLC (IX+d)

- RLC (IY+d)

- RL (HL)

- RL (IX+d)

- RL (IY+d)

- RRC (HL)

- RRC (IX+d)

- RRC (IY+d)

- RR (HL)

- RR (IX+d)

- RR (IY+d)

- SLA (HL)

- SLA (IX+d)

- SLA (IY+d)

- SRA (HL)

- SRA (IX+d)

- SRA (IY+d)

- SET b,(HL)

- SET b,(IX+d)

- SET b,(IY+d)

- RES b,(HL)

- RES b,(IX+d)

- RES b,(IY+d)

- BIT b,(HL)

- BIT b,(IX+d)

- BIT b,(IY+d)

- INI

- IND

- INIR

- INDR

- OUTI

- OUTD

- OTIR

- OTDR

- ADD A,r

- ADC A,r

- SUB r

- SBC A,r

- AND r

- OR r

- XOR r

- CP r

- INC r

- DEC r

- ADD A,n

- ADC A,n

- SUB n

- SBC A,n

- AND n

- OR n

- XOR n

- CP n

- ADD A,(HL)

- ADD A,(IX+d)

- ADD A,(IY+d)

- ADC A,(HL)

- ADC A,(IX+d)

- ADC A,(IY+d)

- SUB (HL)

- SUB (IX+d)

- SUB (IY+d)

- SBC A,(HL)

- SBC A,(IX+d)

- SBC A,(IY+d)

- AND (HL)

- AND (IX+d)

- AND (IY+d)

- OR (HL)

- OR (IX+d)

- OR (IY+d)

- XOR (HL)

- XOR (IX+d)

- XOR (IY+d)

- CP (HL)

- CP (IX+d)

- CP (IY+d)

- INC (HL)

- INC (IX+d)

- INC (IY+d)

- DEC (HL)

- DEC (IX+d)

- DEC (IY+d)

- NEG

- INI

- IND

- INIR

- INDR

- OUTI

- OUTD

- OTIR

- OTDR

- BIT b,r

- BIT b,(HL)

- BIT b,(IX+d)

- BIT b,(IY+d)

- SET b,r

- SET b,(HL)

- SET b,(IX+d)

- SET b,(IY+d)

- RES b,r

- RES b,(HL)

- RES b,(IX+d)

- RES b,(IY+d)

16 ƒrƒbƒg‰‰ژZٹي

- ADD HL,ss

- INIR

- OUTI

- OTIR

- ADD IX,pp

- ADD IY,rr

- INC ss

- INC IX

- INC IY

- INI

- DEC ss

- DEC IX

- DEC IY

- IND

- INDR

- OUTD

- OTDR

ADC HL,ss ‚¾‚¯‚إ‚·پB

SBC HL,ss ‚¾‚¯‚إ‚·پB

- ADD HL,ss

- ADC HL,ss

- SBC HL,ss

- INI

- IND

- INIR

- INDR

- OUTI

- OUTD

- OTIR

- OTDR

DEC ss ‚¾‚¯‚إ‚·پB

- ADD HL,ss

- ADC HL,ss

- SBC HL,ss

- INC ss

- ADD IX,pp

- ADD IY,rr

INC IX ‚¾‚¯‚إ‚·پB

INC IY ‚¾‚¯‚إ‚·پB

- DEC ss

- DEC IX

- DEC IY

- INI

- IND

- INIR

- INDR

- OUTI

- OUTD

- OTIR

- OTDR

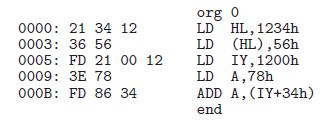

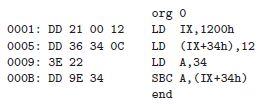

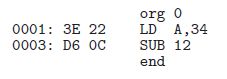

ƒٹƒXƒg1.9.1.1A ADD A,r

|

گ}1.9.1.1A ADD A,r

|

ƒٹƒXƒg1.9.1.2A ADD A,n

|

گ}1.9.1.2A ADD A,n

|

ƒٹƒXƒg1.9.1.3A ADD A,(HL)

|

گ}1.9.1.3A ADD A,(HL)

|

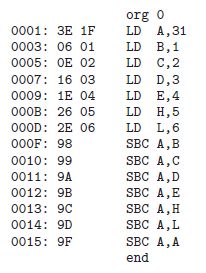

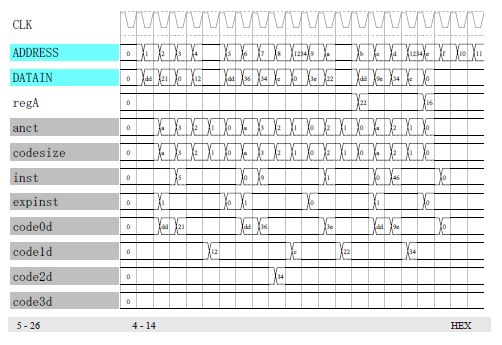

ƒٹƒXƒg1.9.1.4A ADD A,(IX+d)

|

گ}1.9.1.4A ADD A,(IX+d)

|

ƒٹƒXƒg1.9.1.5A ADD A,(IY+d)

|

گ}1.9.1.5A ADD A,(IY+d)

|

ƒٹƒXƒg1.9.1.6A SUB r

|

گ}1.9.1.6A SUB r

|

ƒٹƒXƒg1.9.1.7A SUB n

|

گ}1.9.1.7A SUB n

|

ƒٹƒXƒg1.9.1.8A SUB (HL)

|

گ}1.9.1.8A SUB (HL)

|

ƒٹƒXƒg1.9.1.9A SUB (IX+d)

|

گ}1.9.1.9A SUB (IX+d)

|

ƒٹƒXƒg1.9.1.10A SUB (IY+d)

|

گ}1.9.1.10A SUB (IY+d)

|

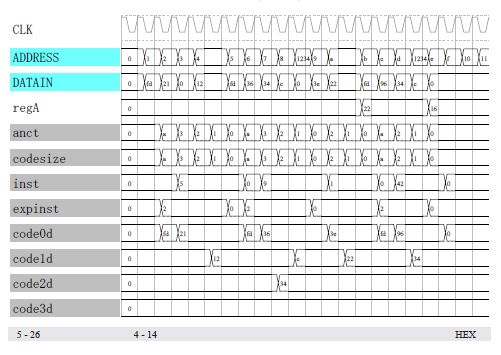

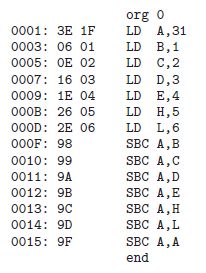

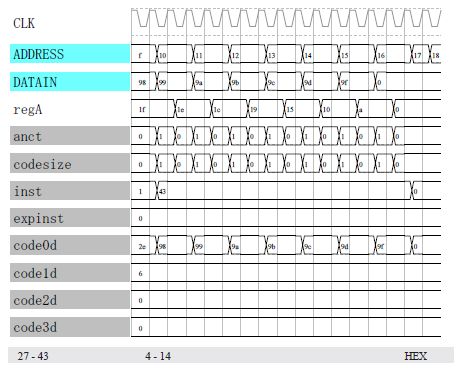

ƒٹƒXƒg1.9.1.11A SBC A,r

|

گ}1.9.1.11A SBC A,r

|

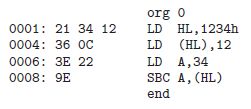

ƒٹƒXƒg1.9.1.12A SBC A,(HL)

|

گ}1.9.1.12A SBC A,(HL)

|

ƒٹƒXƒg1.9.1.13A SBC A,(IX+d)

|

گ}1.9.1.13A SBC A,(IX+d)

|

ƒٹƒXƒg1.9.1.14A SBC A,(IY+d)

|

گ}1.9.1.14A SBC A,(IY+d)

|

ƒٹƒXƒg1.9.1.15A AND r

|

گ}1.9.1.15A AND r

|

ƒٹƒXƒg1.9.1.16A AND n

|

گ}1.9.1.16A AND n

|

ƒٹƒXƒg1.9.1.17A AND (HL)

|

گ}1.9.1.17A AND (HL)

|

ƒٹƒXƒg1.9.1.18A AND (IX+d)

|

گ}1.9.1.18A AND (IX+d)

|

ƒٹƒXƒg1.9.1.19A AND (IY+d)

|

گ}1.9.1.19A AND (IY+d)

|

ƒٹƒXƒg1.9.1.20A OR r

|

گ}1.9.1.20A OR r

|

ƒٹƒXƒg1.9.1.21A OR n

|

گ}1.9.1.21A OR n

|

ƒٹƒXƒg1.9.1.22A OR (HL)

|

گ}1.9.1.22A OR (HL)

|

ƒٹƒXƒg1.9.1.23A OR (IX+d)

|

گ}1.9.1.23A OR (IX+d)

|

ƒٹƒXƒg1.9.1.24A OR (IY+d)

|

گ}1.9.1.24A OR (IY+d)

|

ƒٹƒXƒg1.9.1.25A XOR r

|

گ}1.9.1.25A XOR r

|

ƒٹƒXƒg1.9.1.26A XOR n

|

گ}1.9.1.26A XOR n

|

ƒٹƒXƒg1.9.1.27A XOR (HL)

|

گ}1.9.1.27A XOR (HL)

|

ƒٹƒXƒg1.9.1.28A XOR (IX+d)

|

گ}1.9.1.28A XOR (IX+d)

|

ƒٹƒXƒg1.9.1.29A XOR (IY+d)

|

گ}1.9.1.29A XOR (IY+d)

|

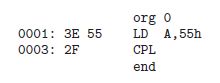

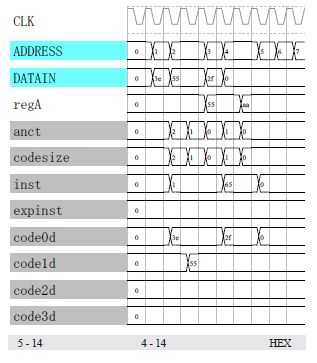

ƒٹƒXƒg1.9.1.30A CPL

|

گ}1.9.1.30A CPL

|

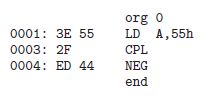

ƒٹƒXƒg1.9.1.31A NEG

|

گ}1.9.1.31A NEG

|

ƒٹƒXƒg1.9.1.32A INC A

|

گ}1.9.1.32A INC A

|

ƒٹƒXƒg1.9.1.33A DEC A

|

گ}1.9.1.33A DEC A

|

ƒٹƒXƒg1.9.1.34A RLCA

|

گ}1.9.1.34A RLCA

|

ƒٹƒXƒg1.9.1.35A RRCA

|

گ}1.9.1.35A RRCA

|

ƒٹƒXƒg1.9.1.36A RLA

|

گ}1.9.1.36A RLA

|

ƒٹƒXƒg1.9.1.37A RRA

|

گ}1.9.1.37A RRA

|

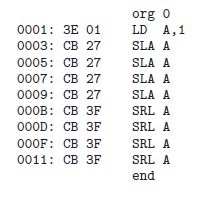

ƒٹƒXƒg1.9.1.38A RL A

|

گ}1.9.1.38A RL A

|

ƒٹƒXƒg1.9.1.39A RR A

|

گ}1.9.1.39A RR A

|

ƒٹƒXƒg1.9.1.40A RLC A

|

گ}1.9.1.40A RLC A

|

ƒٹƒXƒg1.9.1.41A RRC A

|

گ}1.9.1.41A RRC A

|

ƒٹƒXƒg1.9.1.42A SLA A

|

گ}1.9.1.42A SLA A

|

ƒٹƒXƒg1.9.1.43A SRL A

|

گ}1.9.1.43A SRL A

|

ƒٹƒXƒg1.9.1.44A SRA A

|

گ}1.9.1.44A SRA A

|

ƒٹƒXƒg1.9.1.45A SET b,A

|

گ}1.9.1.45A SET b,A

|

ƒٹƒXƒg1.9.1.46A RES b,A

|

گ}1.9.1.46A RES b,A

|